COMPSAC 2017 Plenary Panel Future of Computing: Exciting Research in Computers, Software and Applications <u>Green Multicore Computing</u>

## Hironori Kasahara President Elect 2017, President 2018 IEEE Computer Society

Professor, Dept. of Computer Science & Engineering Director, Advanced Multicore Processor Research Institute Waseda University, Tokyo, Japan URL: http://www.kasahara.cs.waseda.ac.jp/

July 7, 2017 (Friday)

# Performance and Low Power are Key Issues

Power consumption is one of the biggest problems for performance scaling from smartphones to cloud servers and supercomputers ("K" more than 10MW).

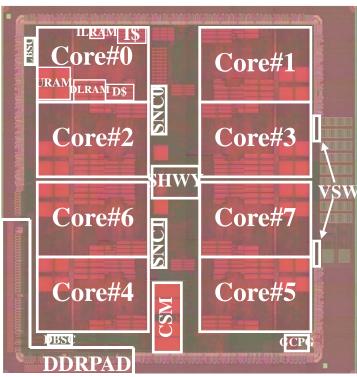

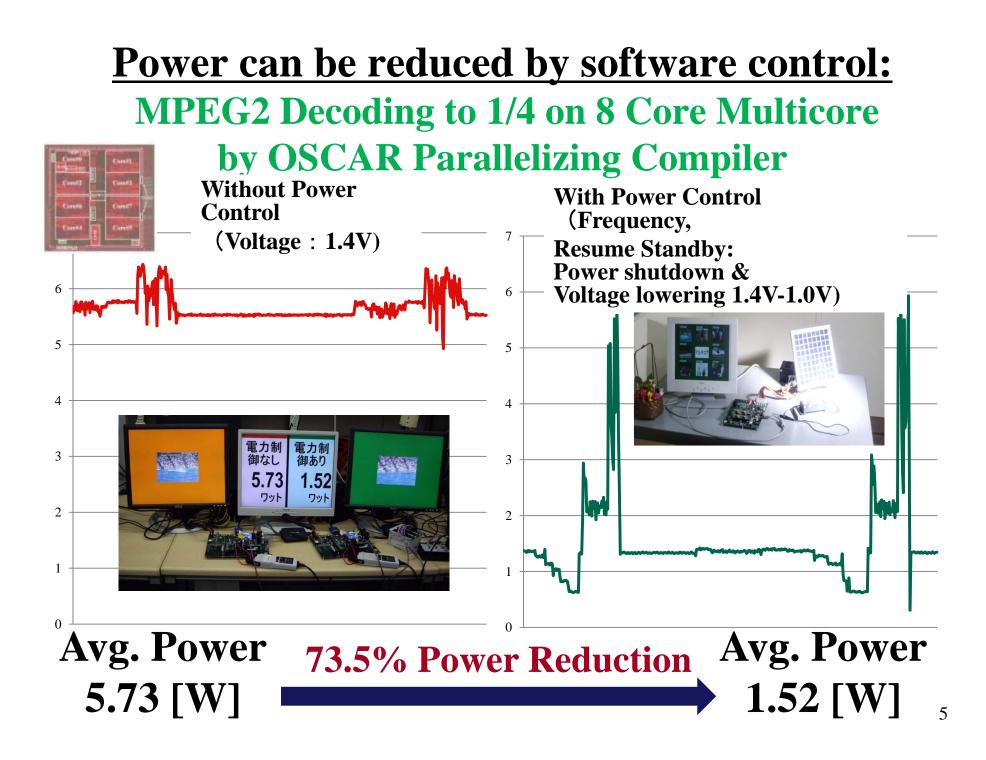

IEEE ISSCC08: Paper No. 4.5, M.ITO, ... and H. Kasahara, "An 8640 MIPS SoC with Independent Power-off Control of 8 CPUs and 8 RAMs by an Automatic Parallelizing Compiler" Power  $\propto$  Frequency \* Voltage<sup>2</sup> (Voltage  $\propto$  Frequency)

▶ Power ∝ Frequency<sup>3</sup>

If <u>Frequency</u> is reduced to <u>1/4</u> (Ex. 4GHz→1GHz), Power is reduced to 1/64 and Performance falls down to <u>1/4</u>. <<u>Multicores</u>> If <u>8cores</u> are integrated on a chip, Power is still <u>1/8</u> and

**<u>Performance</u>** becomes <u>2 times</u>.

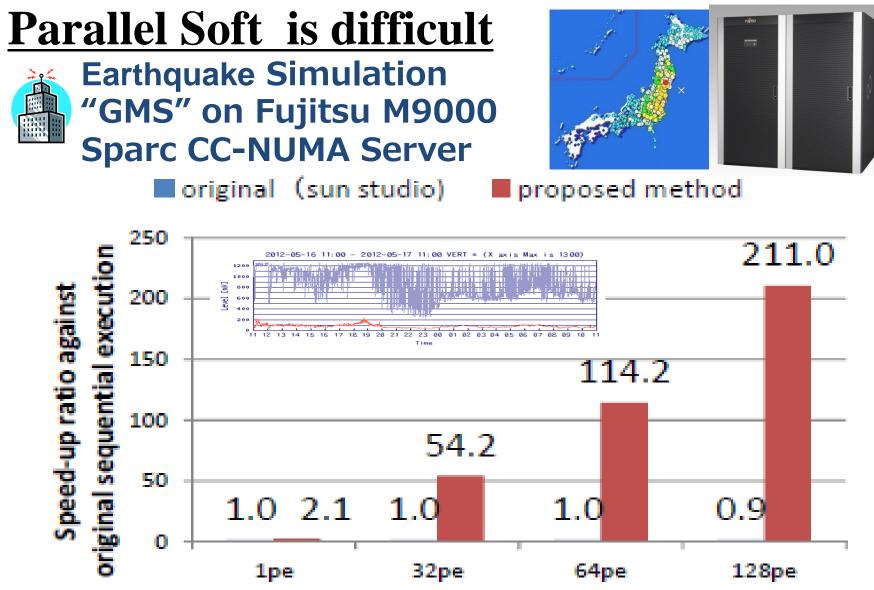

With 128 cores, OSCAR compiler gave us 100 times speedup against 1 core execution and 211 times speedup against 1 core using Sun (Oracle) Studio compiler.

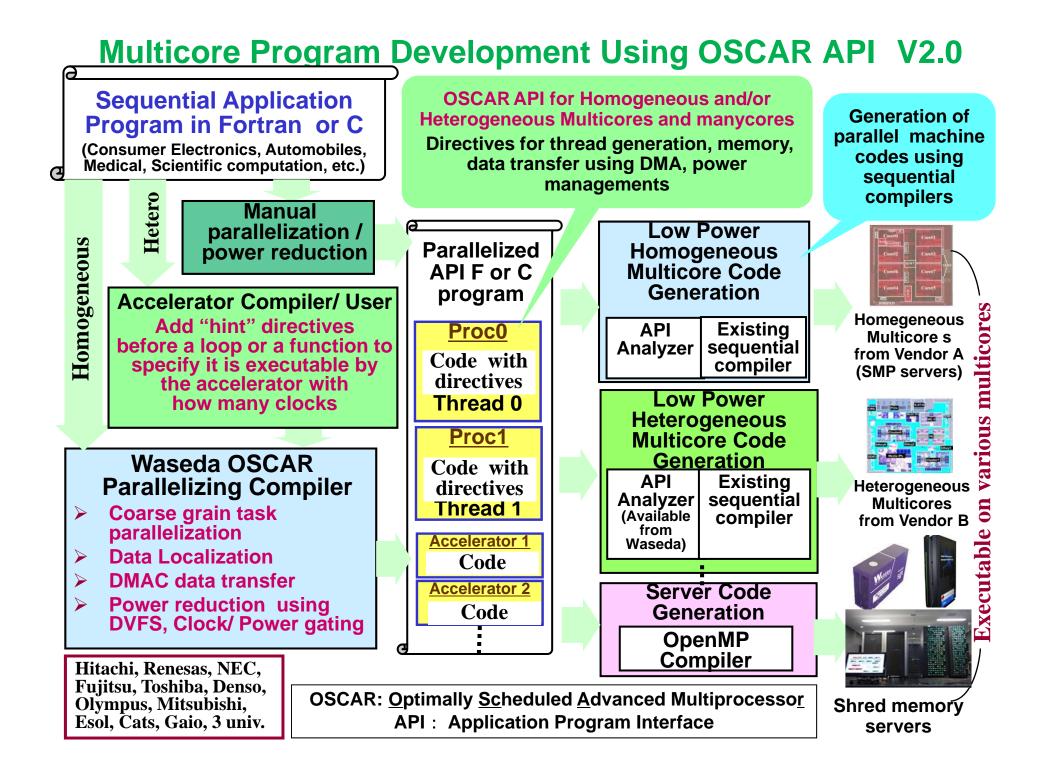

## **OSCAR Parallelizing Compiler**

#### To improve effective performance, cost-performance and software productivity and reduce power

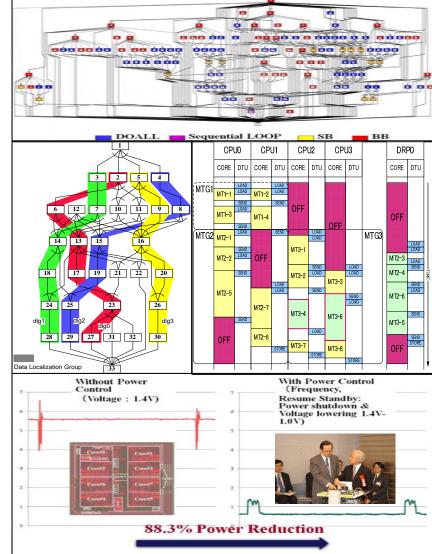

#### **Multigrain Parallelization**

coarse-grain parallelism among loops and subroutines, near fine grain parallelism among statements in addition to loop parallelism

#### **Data Localization**

Automatic data management for distributed shared memory, cache and local memory

#### **Data Transfer Overlapping**

Data transfer overlapping using Data Transfer Controllers (DMAs)

#### **Power Reduction**

Reduction of consumed power by compiler control DVFS and Power gating with hardware supports.

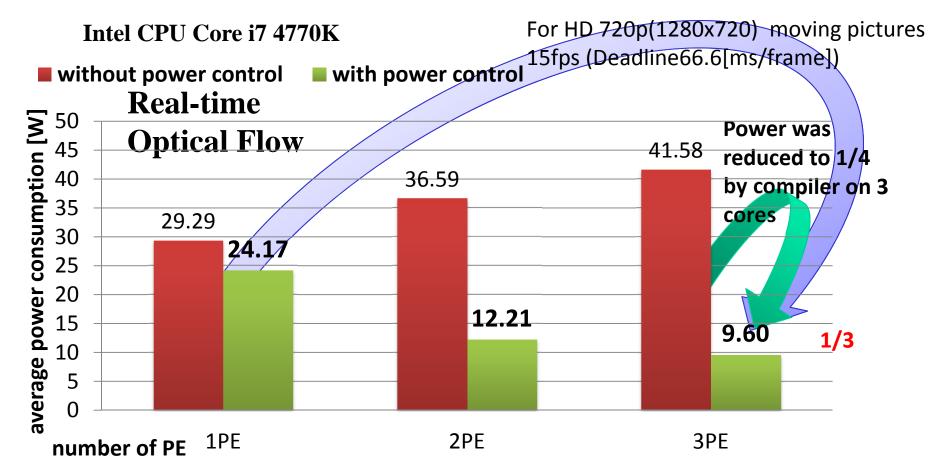

### **Power of Multicores with DVFS can be Reduced by Software: Intel Haswell**

**1 core Power (29.3W)** was reduced to **1/3 (9.6W) with 3 cores by OSCAR compiler.**

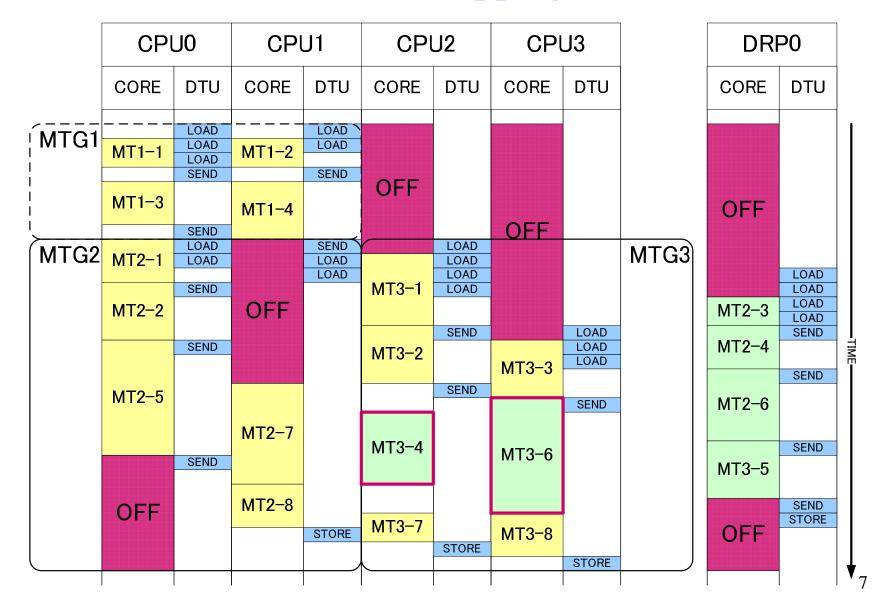

#### An Image of Static Schedule for Heterogeneous Multicore with Data Transfer Overlapping and Power Control

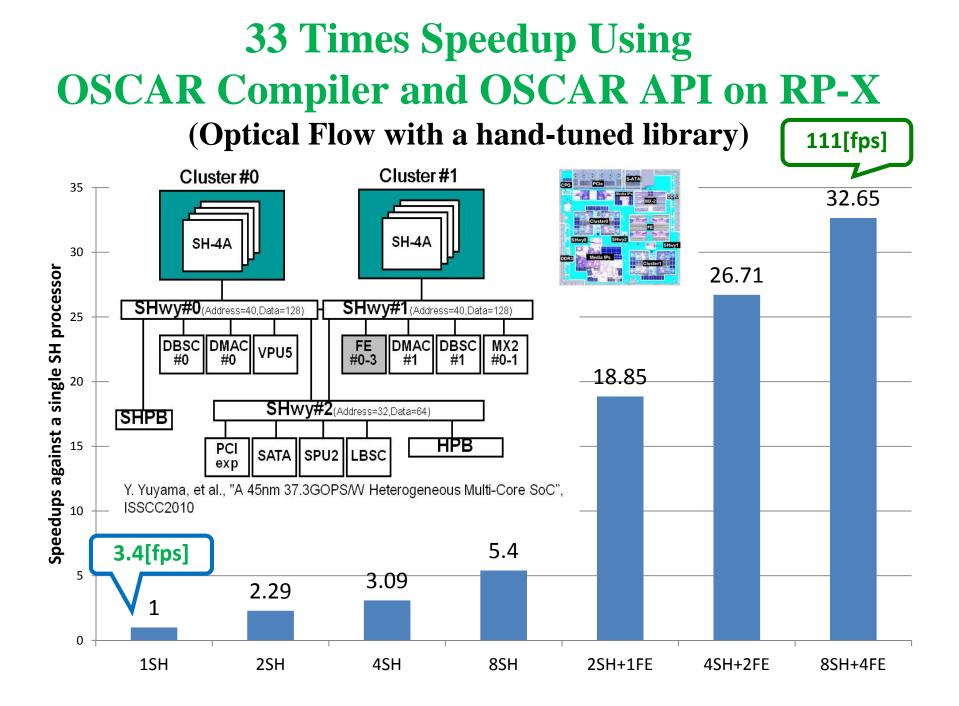

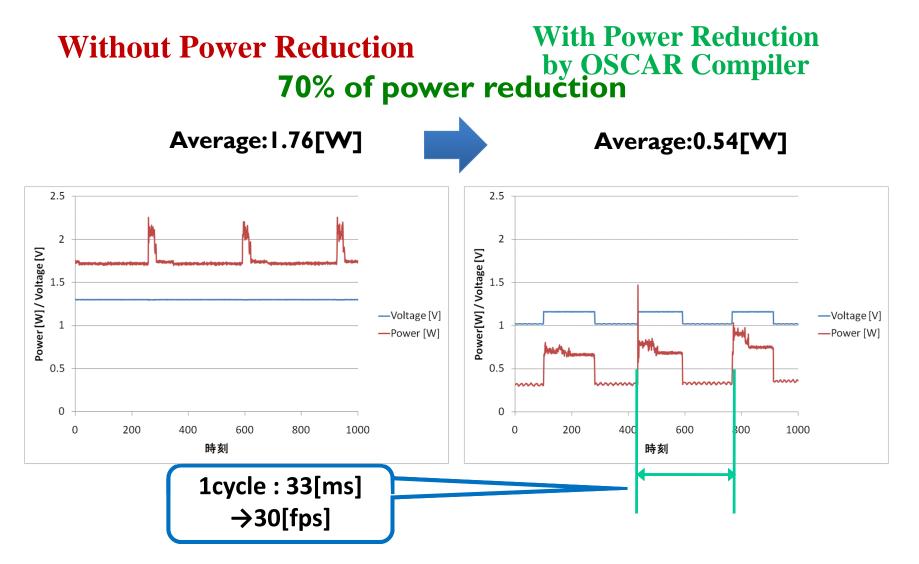

Power Reduction in a real-time execution controlled by OSCAR Compiler and OSCAR API on RP-X (Optical Flow with a hand-tuned library)

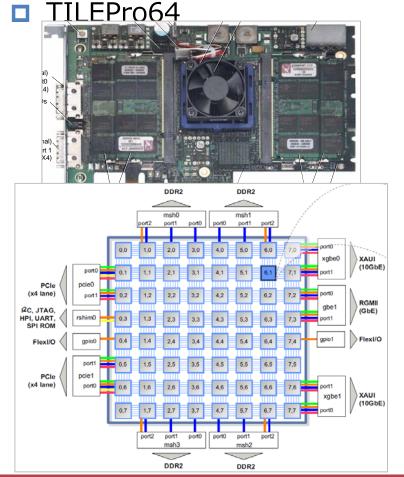

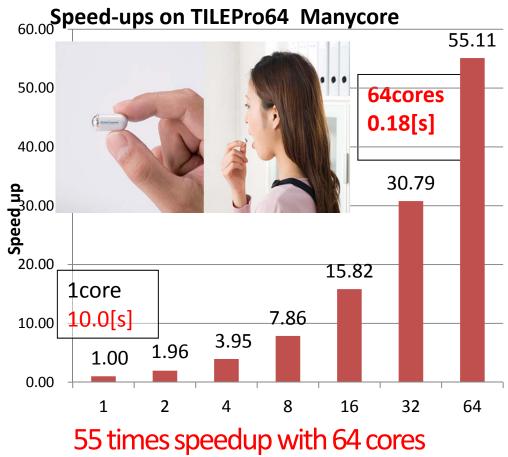

Automatic Parallelization of JPEG-XR for Drinkable Inner Camera (Endo Capsule) 10 times more speedup needed after parallelization for 128 cores of Power 7. Less than 35mW power consumption is required.

Waseda U. & Olympus

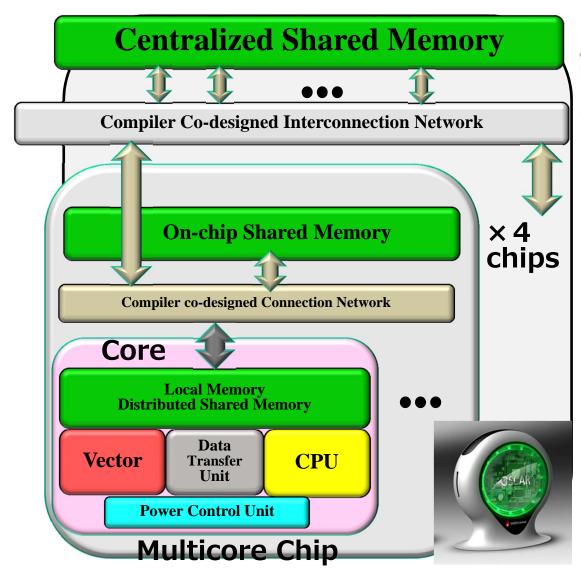

### Architecture Design to Support for Parallelization and Power Reduction by Compiler

**Vector Multicore for Embedded to Severs**

Target:

Solar Powered with

compiler power reduction.

Fully automatic

parallelization and

vectorization including

local memory management and data transfer.

## **Summary**

- Software can further reduce the power consumption of low power processor hardware.

- To develop the parallel software with low development cost and period, automatic paralleling compiler is requires.

- Co-design of compilers and architectures will be more important.

- For example, designing compiler looking at applications first and designing multicore system architectures would be promising.