# 低消費電力リアルタイム処理用ホモジニアス/ ヘテロジニアス・マルチコアと自動並列化コンパイラ 及びマルチプラットフォーム用API

### 早稲田大学

### 理工学術院基幹理工学部情報理工学科 教授 アドバンスト・マルチコア・プロセッサ研究所 所長 IEEE Computer Society理事

#### 笠原博徳

1985年 早稲田大学博士課程了 工学博士 カリフォルニア大学バークレー客員研究員 日本学術振興会第1回特別研究員 1986年 早大理工専任講師, 1988年 助教授 1997年 教授、現在 理工学術院情報理工学科 1989年~1990年 イリノイ大学Center for Supercomputing R&D客員研究員 2009年 IEEE Computer Society 理事 (Golden Core Member 2010-)

<u> 査読付論文 183件</u>, シンポジウム論文 27件, 研究会論 文 125件, 全国大会論文 154件, 招待講演100件, <u>新聞・</u> <u>Web記事・TV等メディア掲載 432件</u>

#### 受賞

1987年 IFAC World Congress Young Author Prize 1997年 情報処理学会坂井記念特別賞 2005年 STARC(半導体理工学研究センタ)共同研究賞 2008年 LSI・オブ・ザ・イヤー 2008 準グランプリ 2008年 Intel Asia Academic Forum Best Research Award 2009年IEEE Computer Society Golden Core Award

#### 政府•学会委員等歴任数 220件

【経済産業省・NEDO他】 45件 【内閣府】 8件 【文部科学省・JST・JSPS・JAXA・原子力機構・海洋研】30件 IEEE 21件, 情報処理学会 36件, ACM 14件, 国際会議PC等 57 件,高校生科学技術チャレンジ審査委員等 他9件

公益社団法人 自動車技術会 第5回 自動車制御とモデル研究専門委員会 2011年6月8日(水)

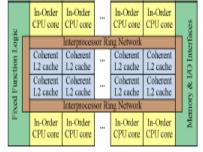

#### マルチコア/メニーコアEverywhere

- 組込からスパコンまで高性能・低消費電力化

- ▶情報家電用マルチコア

カーナビ,携帯電話,ゲーム,デジタルTV, DVD

IBM/ Sony/ Toshiba Cell, Fujitsu FR1000, Panasonic Uniphier, NEC/ARM MPCore/MP211/NaviEngine, Renesas 4 core RP1, 8 core RP2, 15core Hetero RP-X.Plurarity HAL 64(#Marvell)-cores, Tilera Tile64/-Gx100 (→1000cores), DARPA UHPC (2017: 80GFLOPS/W)

#### ▶PC,サーバ

Intel Quad Xeon, Core 2 Quad, Nehalem(8core), 80 core, Larrabee (32core) SCC (48 core), Knights Corner (50 core以上:22nm), AMD 12 Core Opteron, 米Dell:大規模データ・センター用省電力型サーバ:ARMマルチコ アロセッサ (Marvell4コア)

**►**WSs, Deskside & Highend Servers

IBM Power 7(8cores), Cycrops64 (160 cores), Sun Rock (16 cores), Rainbow Falls (16 cores), Fujitsu SPARC64 VIII fx (8 cores)

#### ▶スーパーコンピュータ

IBM 低消費電力マルチコアベースBG/P PowerPC450 (4 cores), BG/Q (A2:16cores) 水冷20PFLOPS, 3-4MW (2011-12), BlueWaters(HPCS) Power7, 10 PFLOP以上(2011.07), 中国Tianhe-1A (4.7PFLOPS,6coreX5670+ Nvidia Tesla M2050), Godson-3B (1GHz40W8core128GFLOPS) -T (64 core, 192GFLOPS:2011)

- ■低消費電力、アプリケーションソフトの充実、短期間 システム開発,低コスト, 高機能化が市場競争力決定 <例>携帯電話,ゲーム,自動車,サーバ

- 並列化コンパイラ協調型メニーコアプロセッサ必要

ルネサス、日立、東工大 早大 RP-X

Intel Larrabee

**IBM** BG/O Proc. **Board**

Tianhe-1A:4.7P(2.56P)FLOPS, No.1, Nov.2010

### NEDOリアルタイム情報家電用マルチコア技術

- <目的>DVD,デジタルTV,カーナビ,携帯電話等リアルタイム情報家電における優位化製品創出を目指したプロセッサ技術の国際競争力強化

- 〈研究期間〉平成17年7月~平成20年3月

- <内容> 下記特徴をもつマルチコア·アーキテクチャ及びコンパイラ技術の確立

- ・優れた価格性能

- ・短ハードウェア・ソフトウェア開発期間

- •低消費電力

- 同一アーキテクチャでローエンドからハイエンド製品まで柔軟に対応

- ・集積度向上に対するスケーラブルな性能向上(複数半導体世代に対応)

- ・異なる企業開発のマルチコア間でのアプリケーションの共用

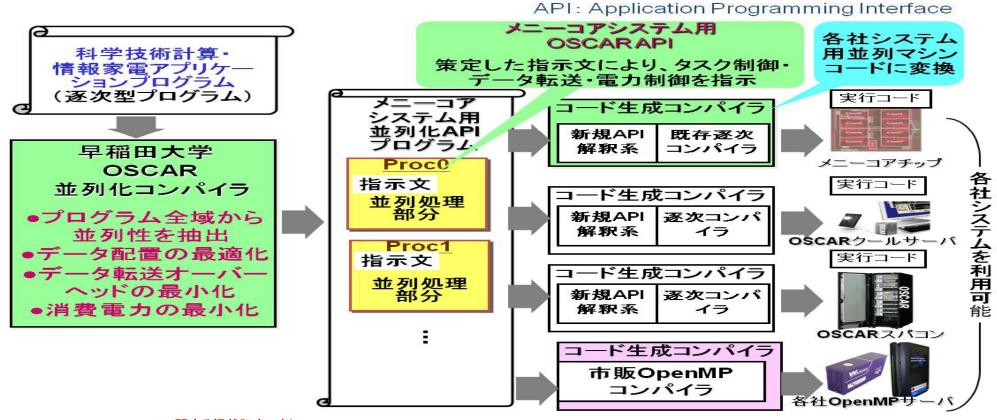

<API: Application Programming Interface並列化コンパイラと各マルチコアの接続>

日立,富士通,ルネサス,東芝,松下,NEC

- 〈委託事業〉NEDO"アドバンスト並列化コンパイラ"の成果と参加各社のプロセッサ技術を 委員会及び研究により発展させ、標準的マルチコア・アーキテクチャと並列化APIを策 定し、既存及び新規チップ上での性能評価を通し改良する

- 〈助成事業〉委託事業にて策定されたアーキテクチャをベースとしたチップ及びその開発環境を開発し委託研究での評価のために供与する

〈PC用プロセッサとの目的の違い〉

リアルタイム処理なアーキテクチャ・自然冷却可能な低消費電力性

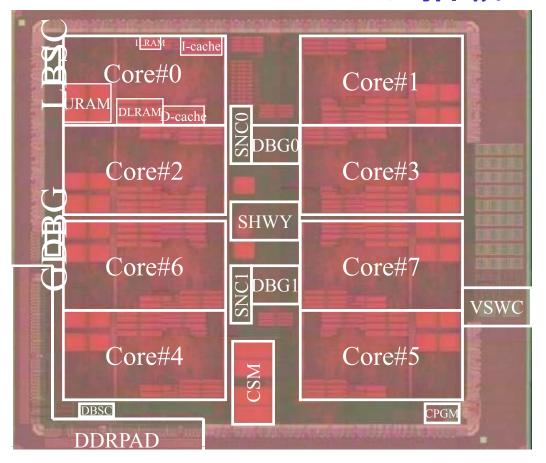

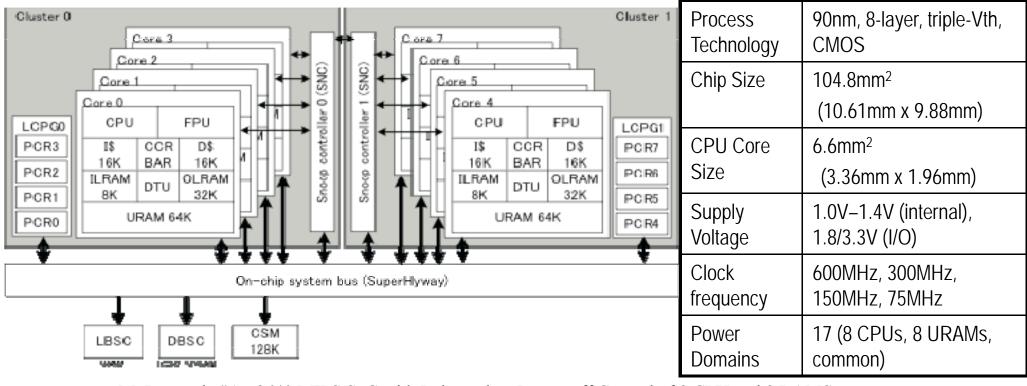

# 早稲田OSCARコンパイラ協調型アーキテクチャ RP2 8コア搭載マルチコアLSI

8コア集積マルチコアLSIチップ写真

| プロセス                              | 90nm CMOS, 8層メタル, 3種Vth                                                                                                                                                                                      |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| チップ <sup>°</sup> サイス <sup>*</sup> | 104.8mm² (10.61mm x 9.88mm)                                                                                                                                                                                  |

| 電源電圧                              | 1.0V-1.4V(¬७), 1.8/3.3V(I/O)                                                                                                                                                                                 |

| 動作周波数                             | 600MHz                                                                                                                                                                                                       |

| CPU性能                             | 8640 MIPS (Dhrystone 2.1)                                                                                                                                                                                    |

| FPU性能                             | 33.6 GFLOPS                                                                                                                                                                                                  |

| 低電力制御                             | <ul> <li>・CPU毎に独立した周波数変更</li> <li>・CPUコアのクロックを停止するスリープモード</li> <li>・CPUコアの一部のクロックを停止するがキャッシュコヒーレンシ維持可能なライトスリープモード</li> <li>・CPUコアの電源供給を停止するフル電源遮断モード</li> <li>・URAM以外のCPUコアの電源供給を停止するレジューム電源遮断モード</li> </ul> |

ISSCC08発表: ISSCC08 論文番号4.5, M.ITO, et al., "An 8640 MIPS SoC with Independent Power-off Control of 8 CPUs and 8 RAMs by an Automatic Parallelizing Compiler"

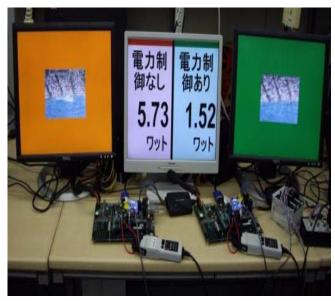

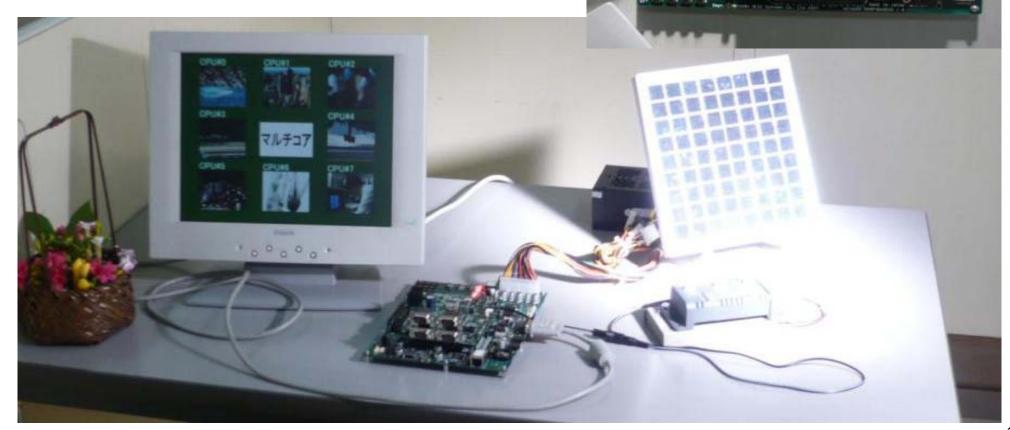

#### NEDOリアルタイム情報家電用マルチコアチップ・デモの様子

http://www8.cao.go.jp/cstp/gaiyo/honkaigi/74index.html

#### 第74回総合科学技術会議【平成20年4月10日】

第74回総合科学技術会議の様子(1)

第74回総合科学技術会議の様子(2)

第74回総合科学技術会議の様子(3)

第74回総合科学技術会議の様子(4)

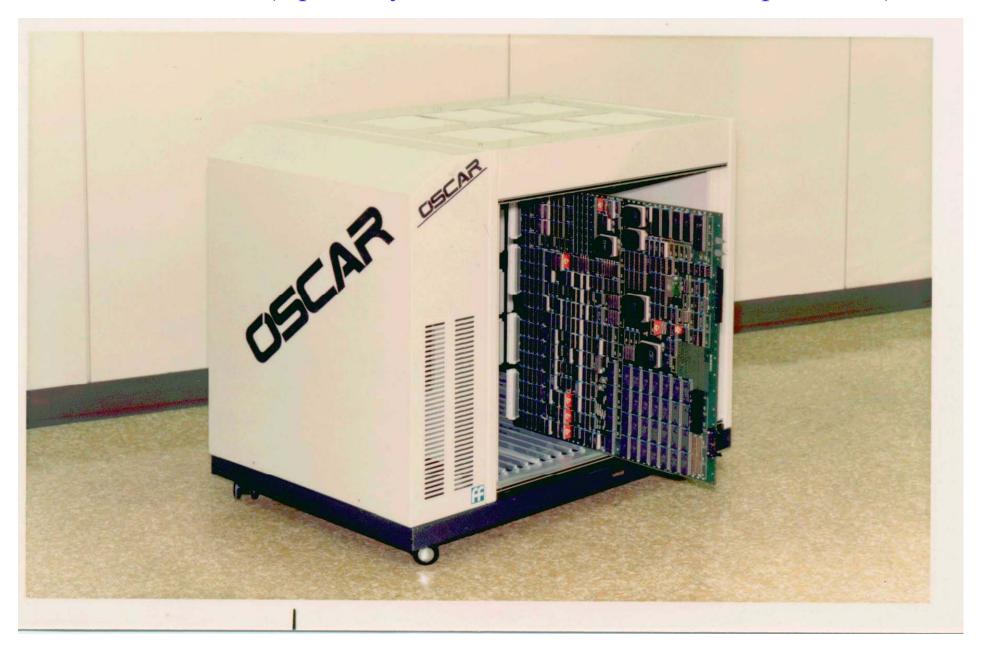

#### 1987 OSCAR(Optimally Scheduled Advanced Multiprocessor)

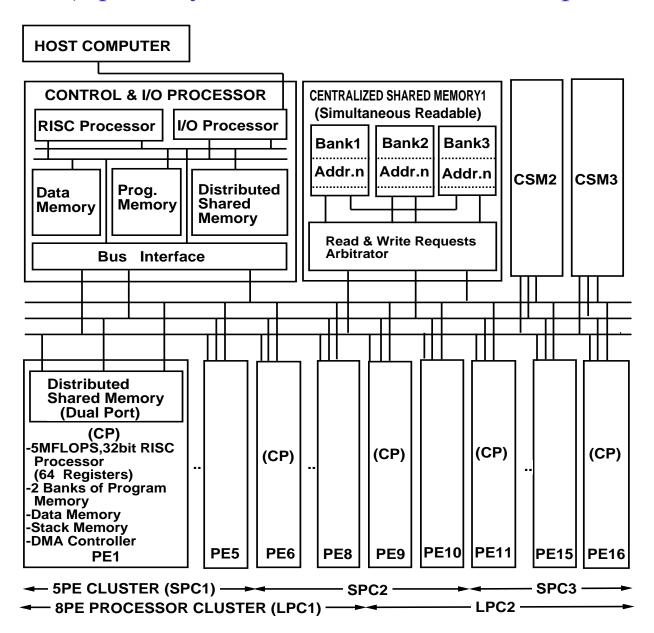

#### OSCAR(Optimally Scheduled Advanced Multiprocessor)

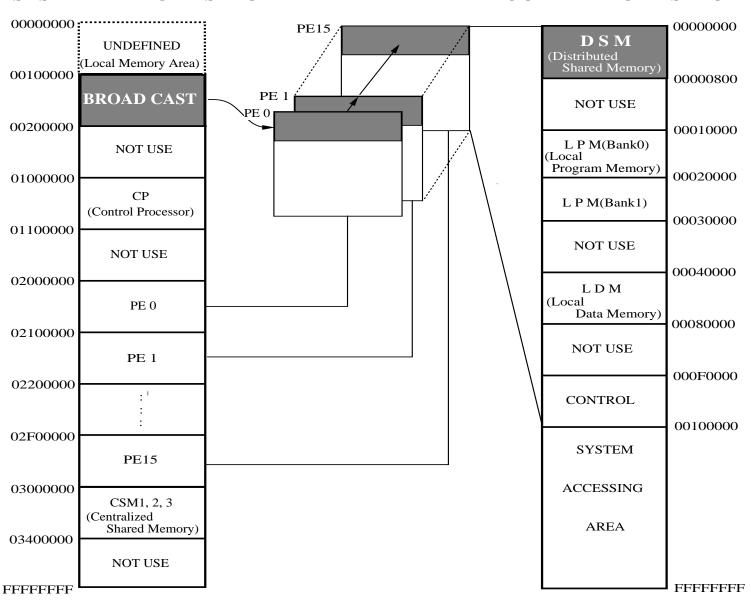

#### OSCAR Memory Space (Global and Local Address Space)

#### SYSTEM MEMORY SPACE

#### LOCAL MEMORY SPACE

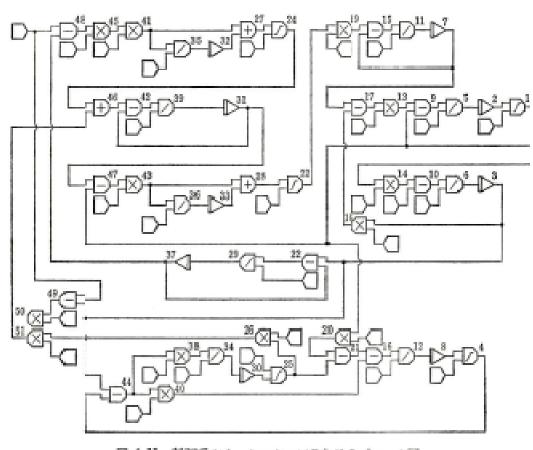

# 1980年代初頭に取り組んだ連続システムシミュレーションの自動並列化:ブロック図をグラフィック入力すると自動的に常微分方程式を自動並列求解

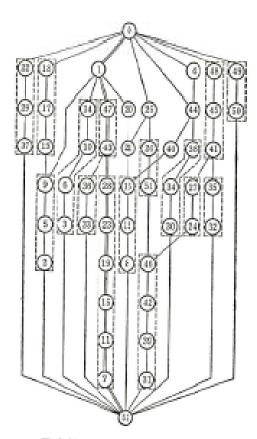

図 4.11 制御系シミュレーションのためのブロック図

図 4.12 図 4.11 カタスタグラフ

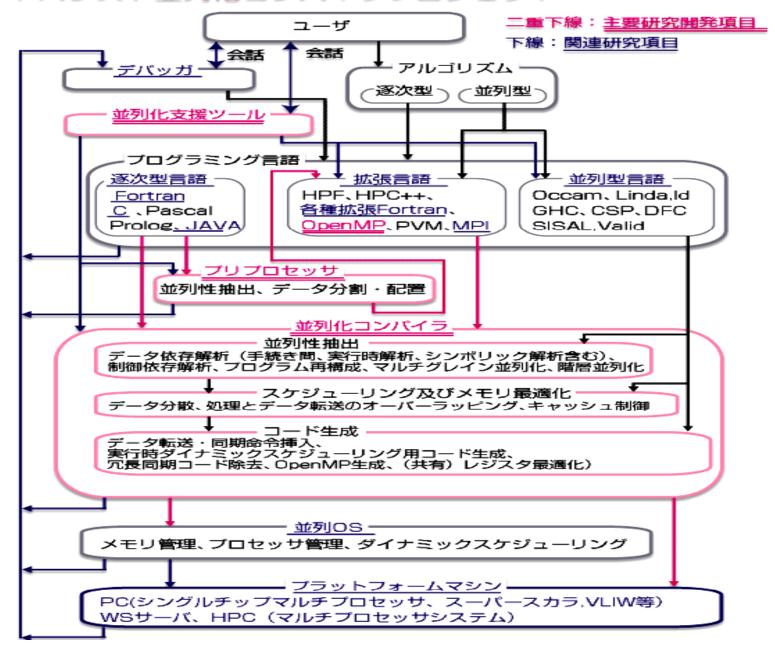

#### アドバンスト並列化コンパイラプロジェクト

# 世界をリードするマルチコア用コンパイラ技術

プロセッサ高速化における3大技術課題の解消

- 1. 半導体集積度向上(使用可能トランジスタ数増大) に対する速度向上率の鈍化

- ▶ 粗粒度タスク並列化、ループ並列化、近細粒度並列化によりプログラム全域の並列性を利用するマルチグレイン並列化機能により、従来の命令レベル並列性より大きな並列性を抽出し、複数マルチコアで速度向上

- 2. メモリウオール問題

- コンパイラによるローカルメモリへのデータ分割配置、DMAコントローラによるタスク実行とオーバーラップしたデータ転送によりメモリアクセス・データ転送オーバーヘッド最小化

- 3. 消費電力増大による速度向上の鈍化

- コンパイラによる低消費電力制御機能を用いたアプリケーション内でのきめ細かい周波数・ 電圧制御・電源遮断により消費電力低減

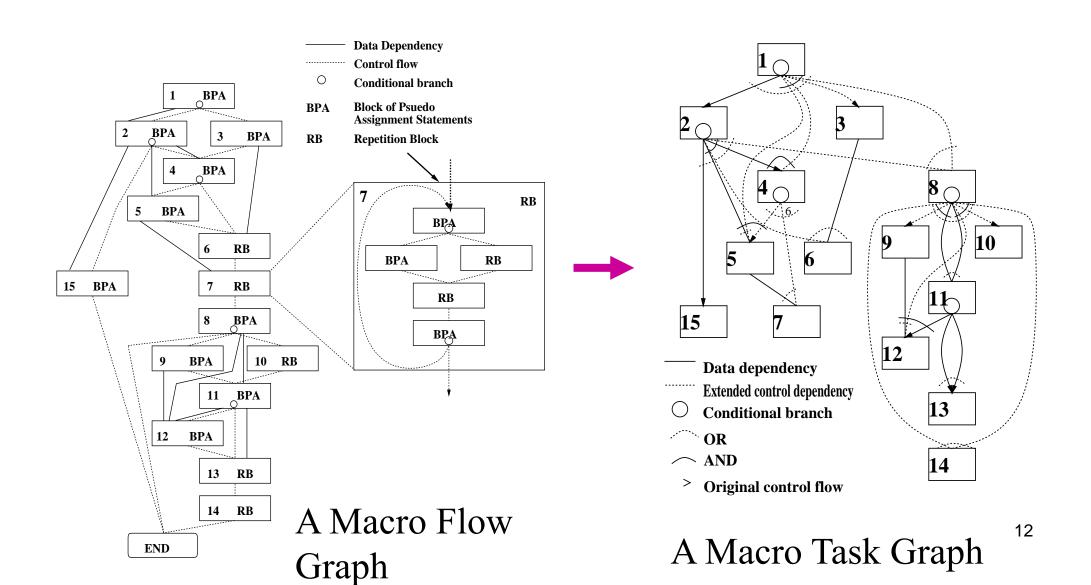

# Earliest Executable Condition Analysis for coarse grain tasks (Macro-tasks)

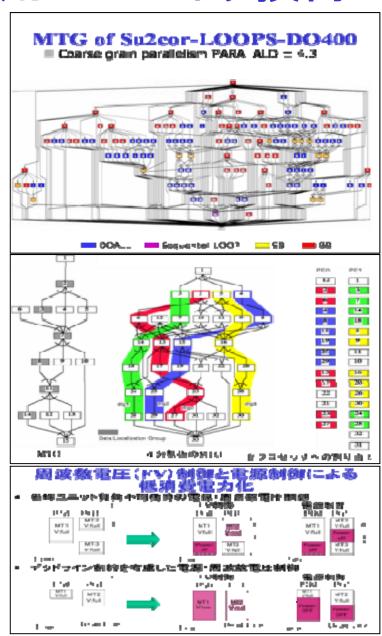

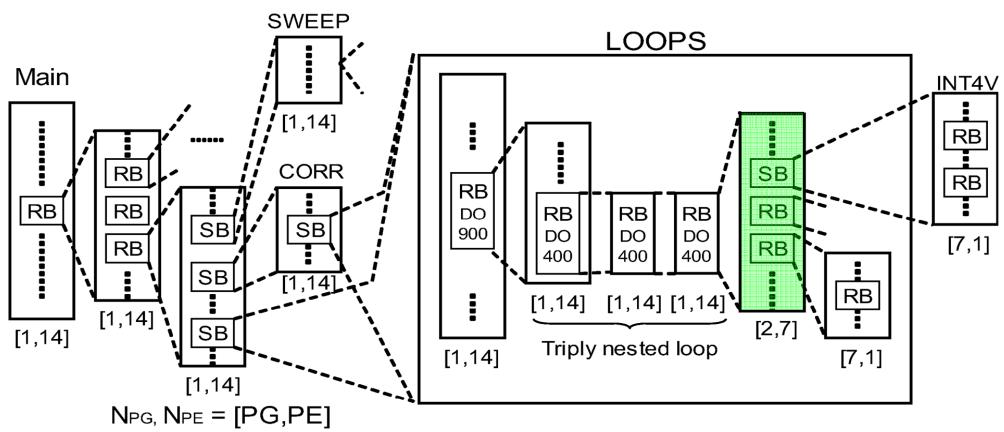

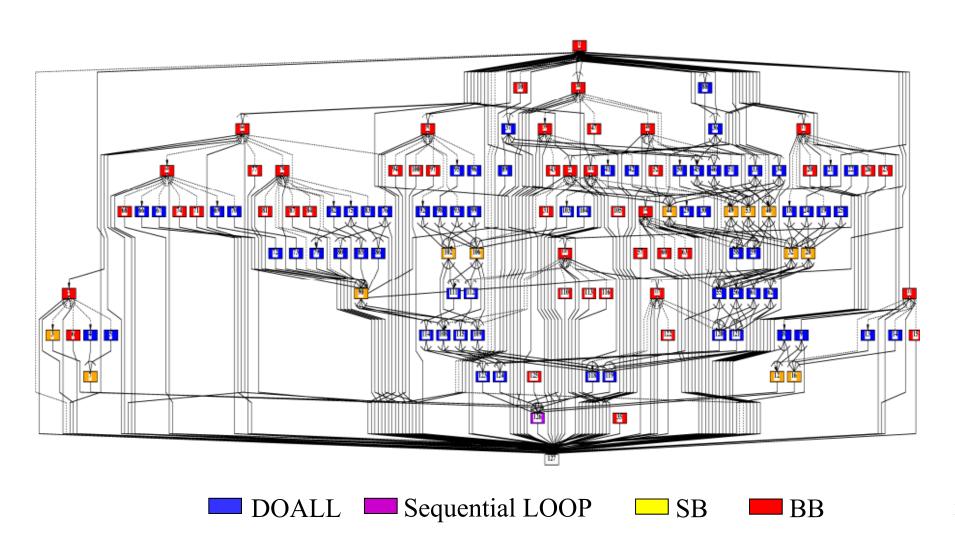

### Automatic processor assignment in su2cor

- Using 14 processors

- Coarse grain parallelization within DO400 of subroutine LOOPS

#### MTG of Su2cor-LOOPS-DO400

$\blacksquare$  Coarse grain parallelism PARA ALD = 4.3

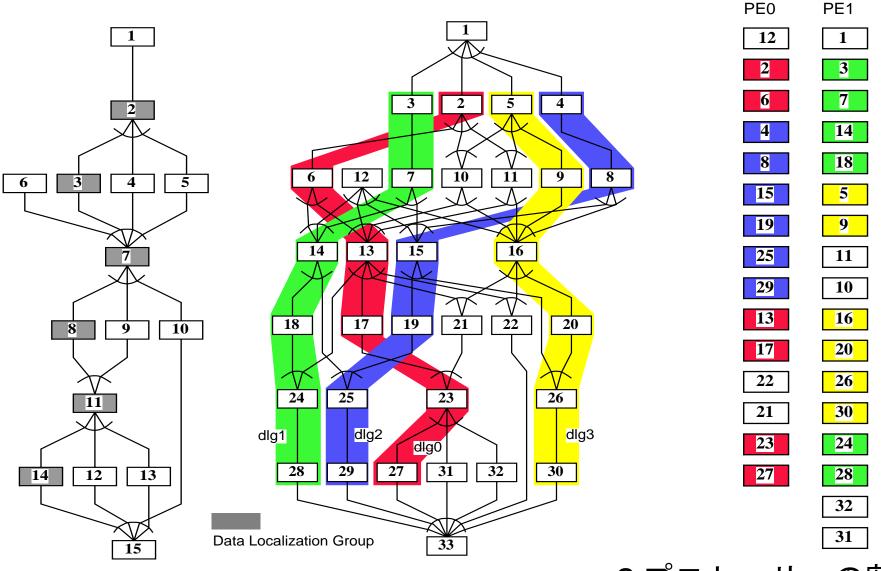

#### データローカライゼーションのイメージ

4分割後のMTG

MTG

2プロセッサへの割り当て

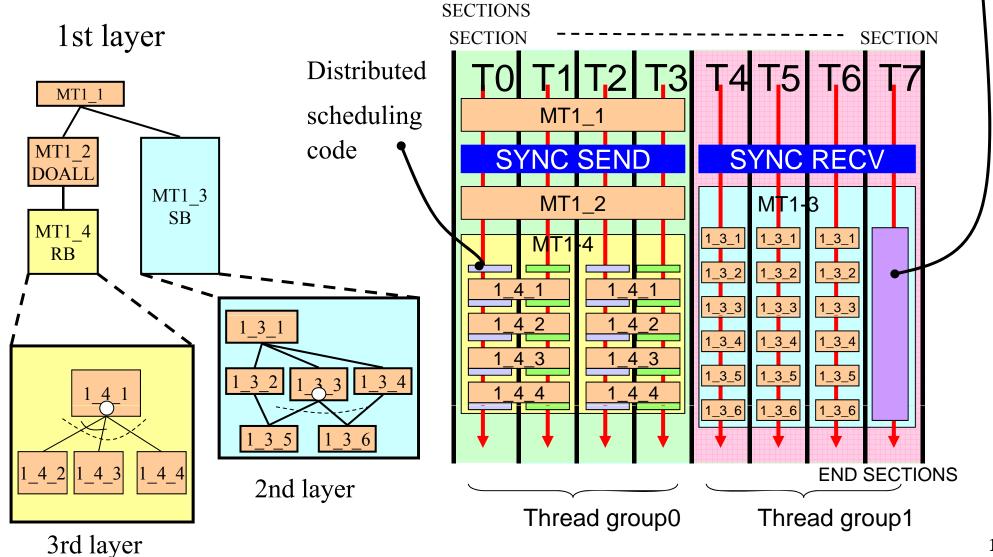

#### OSCARコンパイラが自動生成するマルチコアAPI (OpenMP互換)利用、階層マルチグレイン 並列プログラムのイメージ

Centralized scheduling code

#### デファクトスタンダードを目指すOSCAR マルチコア・メニーコアAPI

IT・半導体6社と開発したOSCAR マルチコア APIはhttp://www.kasahara.cs.waseda.ac.jp/にて公開組込からハイエンドまで各社のマルチコア(ホモジニアス/ヘテロジニアスアーキテクチャ)上で動作可能本センターでは自動車・情報家電・ツールメーカを含め11社と共に研究開発

#### OSCAR マルチコアAPI に関する掲載記事の例

- 1. 日経産業新聞「情報家電用マルチコアMPU 並列処理で消費電力低減 国家プロジェクトで成果 日本勢の武器に」, Jan. 16. 2009.

- 2. 日経産業新聞「早大 マルチコアMPU効率利用 プログラム仕様公開」, Nov. 12. 2008.

- 3. 日本経済新聞「情報家電向けの並列処理ソフト 早大・日立などが開発」, Jun. 01. 2007.

- 4. EDN Japan, No.95, pp.17「並列化コンパイラ「OSCAR」向けのAPI、各社マルチコア用コードの自動生成が可能に」, Jan. 01. 2009.

- 5. Automotive Electronics, 2008年第2号, 「間近に迫るマルチコアプロセッサ時代」, May. 01. 2008.

- 6. EDN Japan MAGAZINE ARTICLES, 2009年1月号「並列化コンパイラ「OSCAR」向けのAPI、各社マルチコア用コードの自動生成が可能に」, Jan. 01. 2009.

- 7. 日経エレクトロニクス Tech On 「早大と国内半導体メーカー、並列実行や電力制御をコンパイラに指示する標準APIを策定」、Nov. 14. 2008.

- 8. Nikkei Electronics Tech On "Group Develops Standard API to Give Parallel Execution, Power Control Orders to Compiler", Nov. 16. 2008.

- 9. 日経BP 先端技術事業化「早稲田大学の笠原教授ら、企業6社とのプロジェクトで実時間並列処理向けAPIを開発、2008年11月から公開」, Nov. 14. 2008.

# 公開OSCAR API v1.0の指示文

- ▶ 並列実行API

- parallel sections (\*)

- flush (\*)

- critical (\*)

- execution

- メモリ配置API

- threadprivate (\*)

- distributedshared

- onchipshared

- ▶ 同期API

- groupbarrier

- (\* OpenMPからの指示文)

- ▶ データ転送API

- dma transfer

- dma\_contiguous\_parameter

- dma stride parameter

- dma flag check

- dma flag send

- ▶電力制御API

- fvcontrol

- get fvstatus

- ▶ タイマーAPI

- get current time

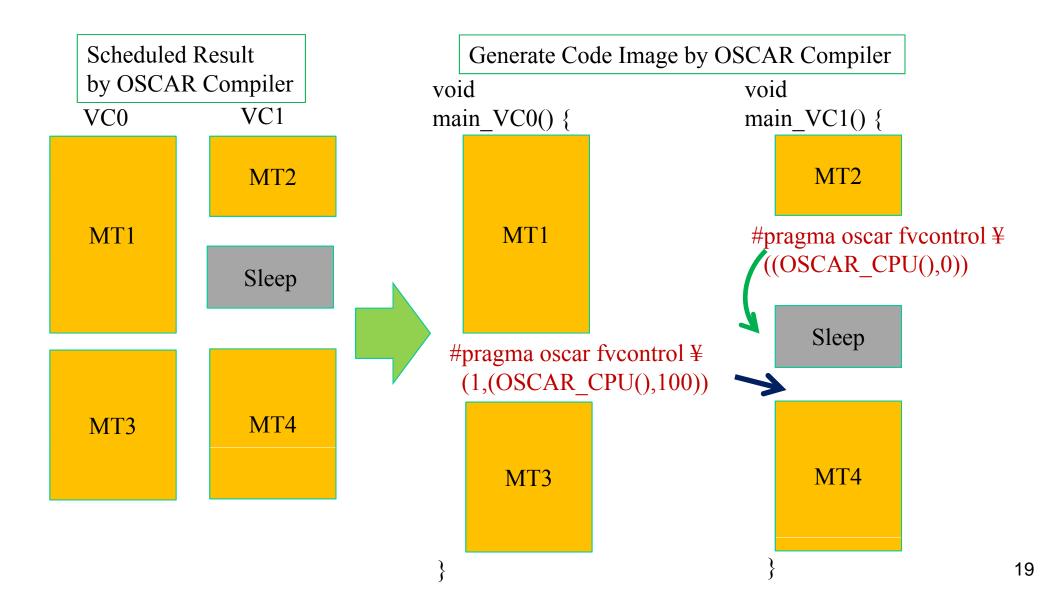

#### **Low-Power Optimization with OSCAR API**

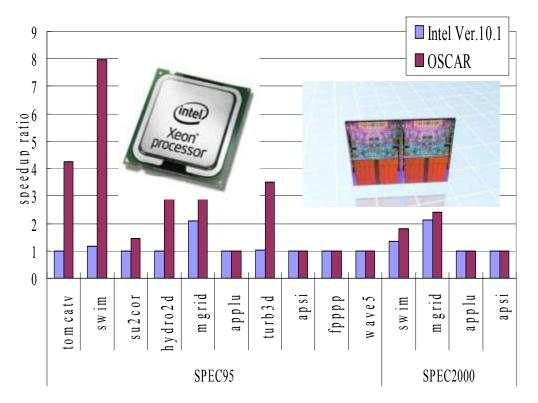

#### 現状:世界最高性能のOSCARコンパイラの性能

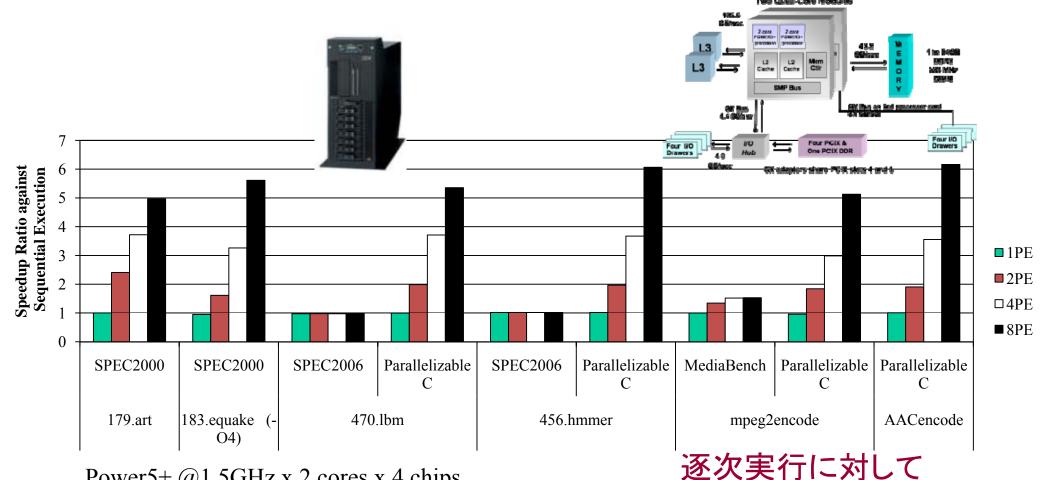

インテル・IBMマルチコアサーバ上でそれぞれ2倍・3倍以上の高速化

### インテル クアッドコアXeonプロセッサ上での 早稲田大学 OSCARコンパイラの性能

インテル・マルチコア上で インテルコンパイラに比べ

2.1 倍速度向上

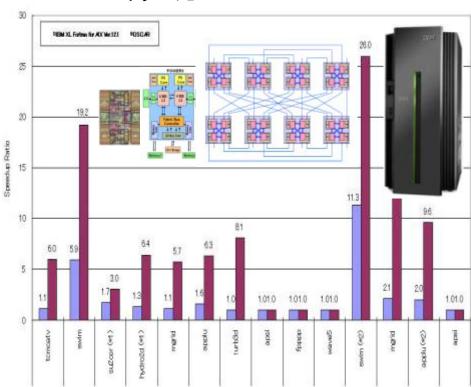

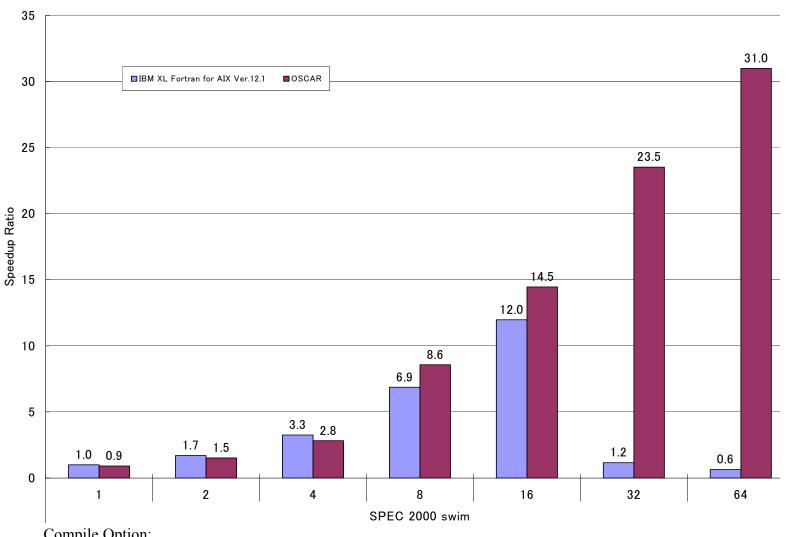

### IBM p6 595 Power6 (4.2GHz) ベース 32コア SMP サーバ上での早稲田大学OSCARコンパイラの性能

IBM最新サーバ上で IBMコンパイラに比べ

**3.3** 倍速度向上

### IBMサーバp550q上でのOSCAR並列化コンパイラの性能

8プロセッサコア・マルチプロセッサシステム上で従来 のループ並列化に対し、2.7倍の高速化 ■ ループ並列化 ■ マルチグレイン並列化 8 speedup ratio 3 tomcatv swim su2cor hydro2d mgrid applu turb3d apsi fpppp wave5 swim mgrid applu spec95 spec2000

# IBM p5 550Q Server (8 コア) におけるCプログラム自動並列化結果

Power5+ @1.5GHz x 2 cores x 4 chips

L1 I\$: 64KB, L1 D\$: 32KB

L2\$: 1.9MB/chip, L3\$: 36MB/chip

SMT: Disabled

平均5.54倍の速度向上

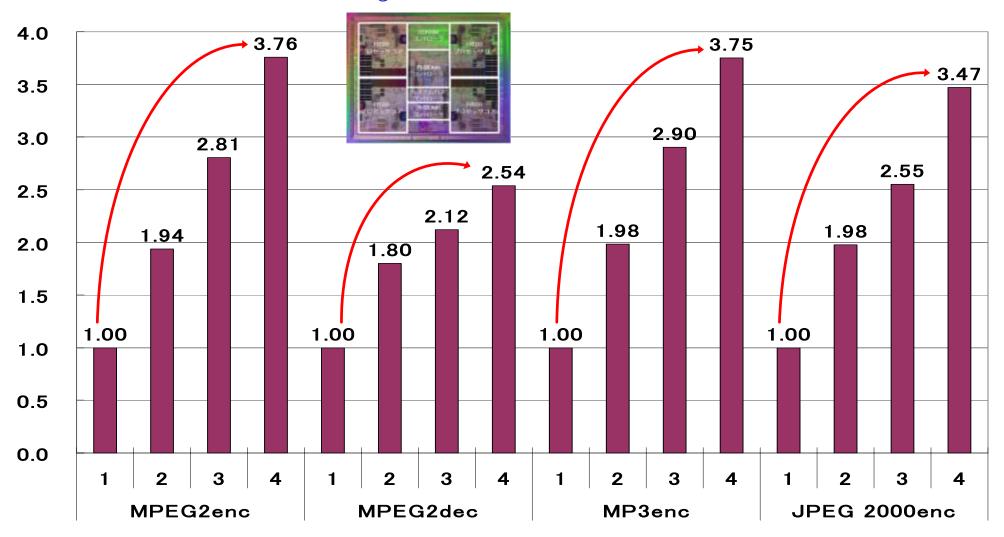

# Performance of OSCAR Compiler Using the multicore API on Fujitsu FR1000 Multicore

3.38 times speedup on the average for 4 cores against a single core execution

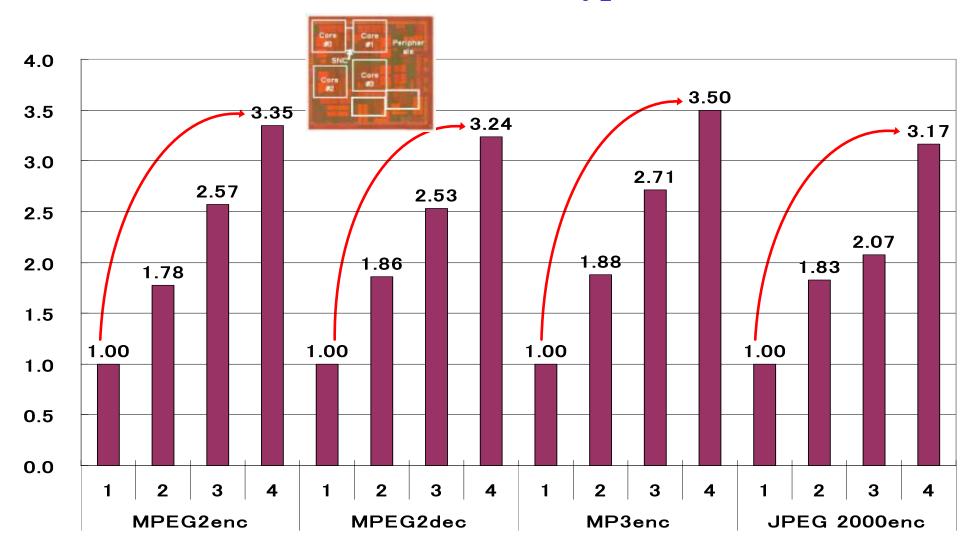

# Performance of OSCAR Compiler Using the Developed API on 4 core (SH4A) OSCAR Type Multicore

3.31 times speedup on the average for 4cores against 1core

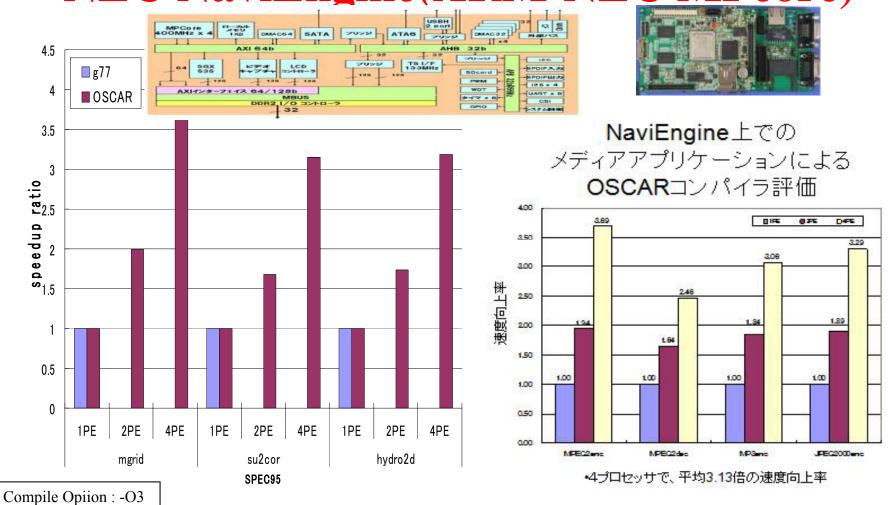

# Performance of OSCAR compiler on NEC NaviEngine(ARM-NEC MPcore)

OSCAR compiler gave us 3.43 times speedup against 1 core for Fortran and 3.13 for C on ARM/NEC MPCore with 4 ARM 400MHz cores

#### 周波数電圧(FV)制御と電源制御による低消費電力化

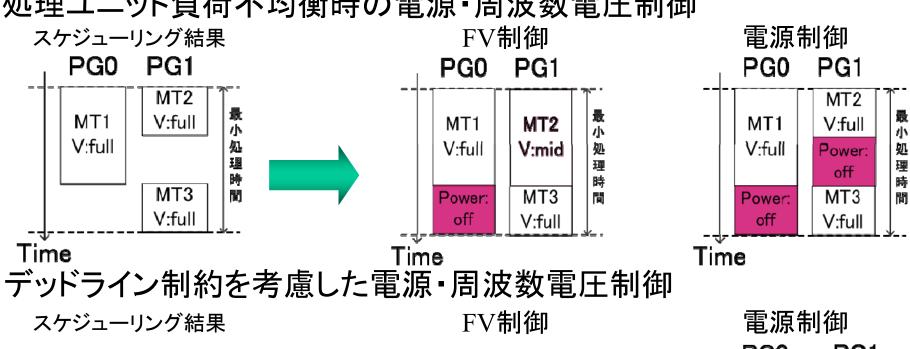

処理ユニット負荷不均衡時の電源・周波数電圧制御

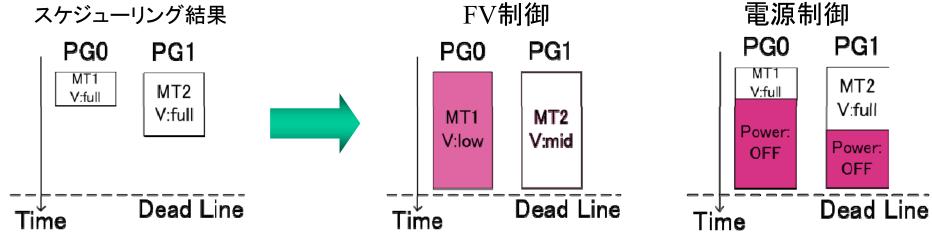

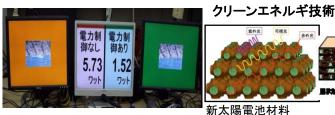

#### 現状:世界唯一コンパイラによる消費電力削減に成功

太陽電池で駆動可

# ソーラパネル駆動可能な 低消費電力高性能マルチコア RP2(SH4A 8コア集積)

- ▶ クリーンエネルギーで駆動可

- ▶電力供給が困難な場所での使用可能

- ▶災害時でも使用可能

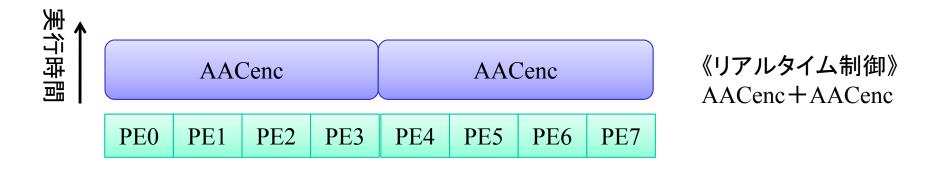

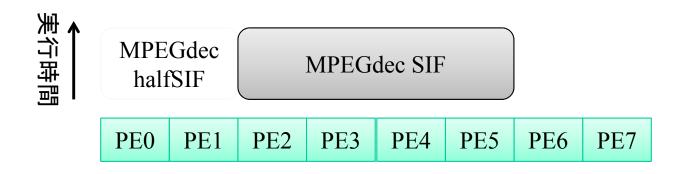

#### RP2上での複数アプリケーション実行時の割り当てイメージ

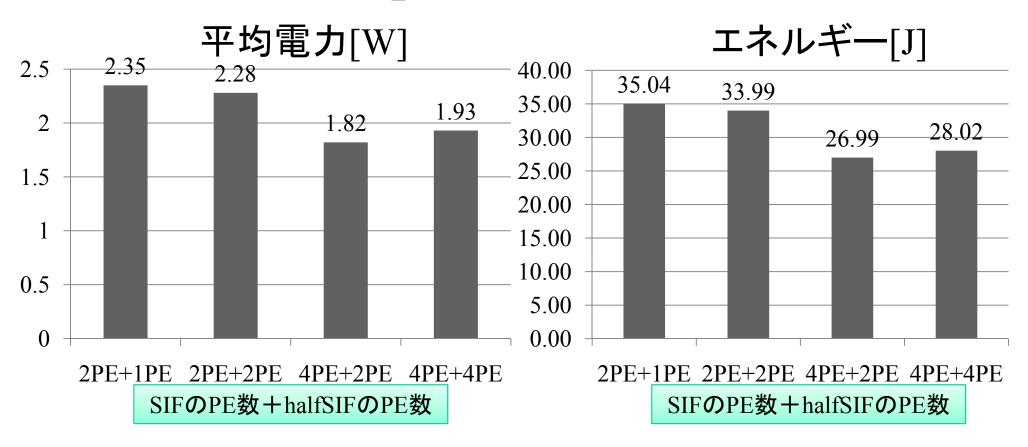

《リアルタイム制御》 MPEG2dec(SIF) +MPEG2dec(halfSIF)

### RP2上でMPEG2dec(SIF+halfSIF)を同時実行させた場合の 電力・エネルギー

- ・SIFサイズは2PE以上、halfSIFサイズは1PE以上でリアルタイム制御可能

- ・4PE+4PEで4PE+2PEと比べ電力が下がらない要因

- ⇒RP2ではチップ全体の電圧を制御するため、SIFとhalfSIFの高い方の電圧が選ばれてしまうため、単独実行では周波数と共に電圧を下げられるのに対して、同時実行では電圧が下がらない

- ■4PE+2PEは周波数を下げるタイミングが合っているため電圧が下がっている

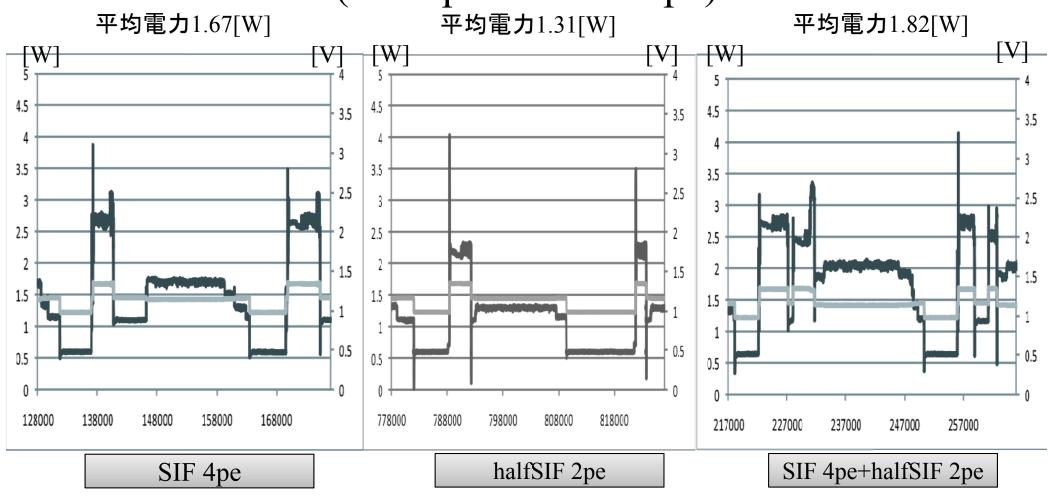

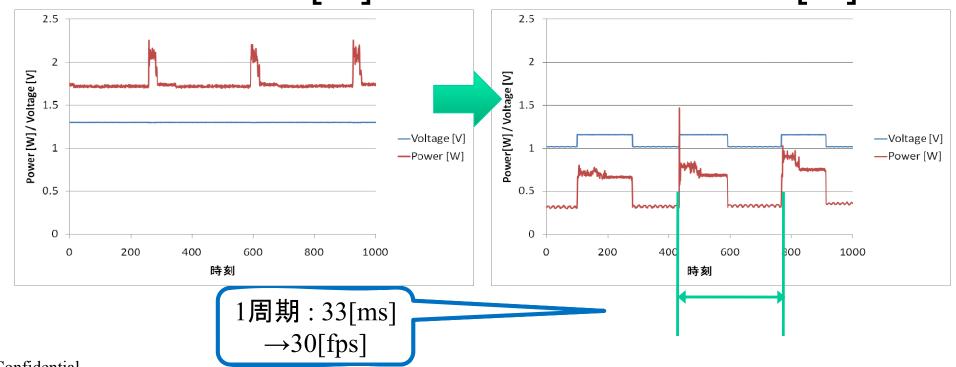

# MPEG2decの電力波形比較 (SIF 4pe・halfSIF 2pe)

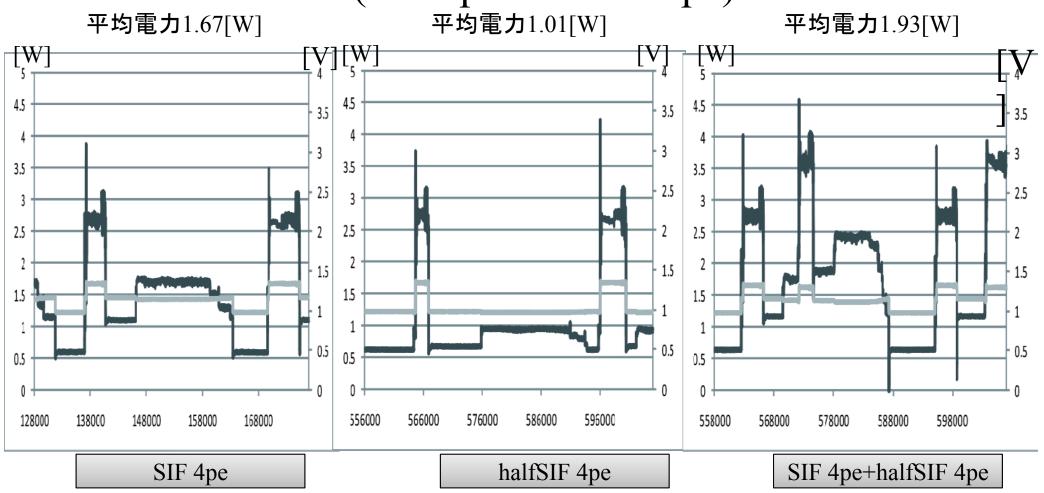

# MPEG2decの電力波形比較 (SIF 4pe・halfSIF 4pe)

・異なる動作のアプリケーションを同時に実行した場合、アプリケーション毎に 低電圧状態となるタイミングが違うため、平均電力が上昇する

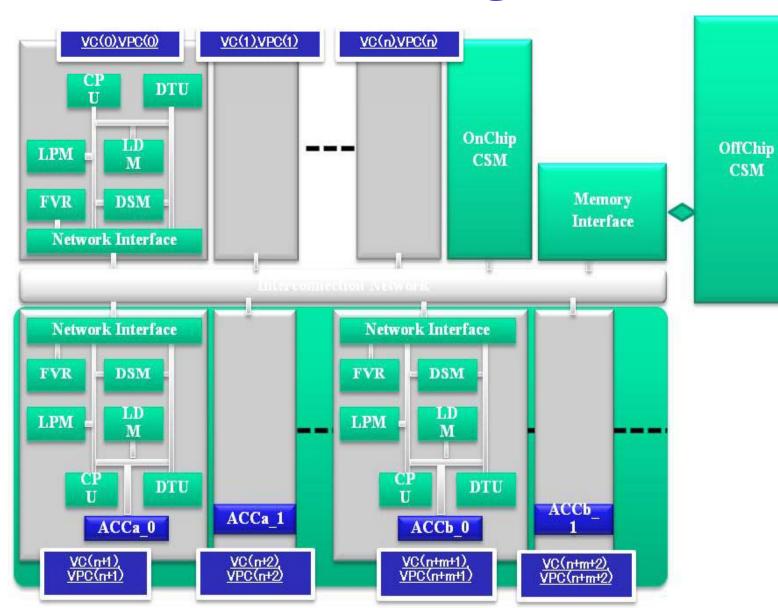

# **OSCAR Heterogeneous Multicore**

#### DTU

Data Transfer Unit

#### LPM

Local Program Memory

#### LDM

Local Data Memory

#### **DSM**

Distributed Shared Memory

#### **CSM**

Centralized Shared Memory

#### **FVR**

Frequency/Voltage Control Register

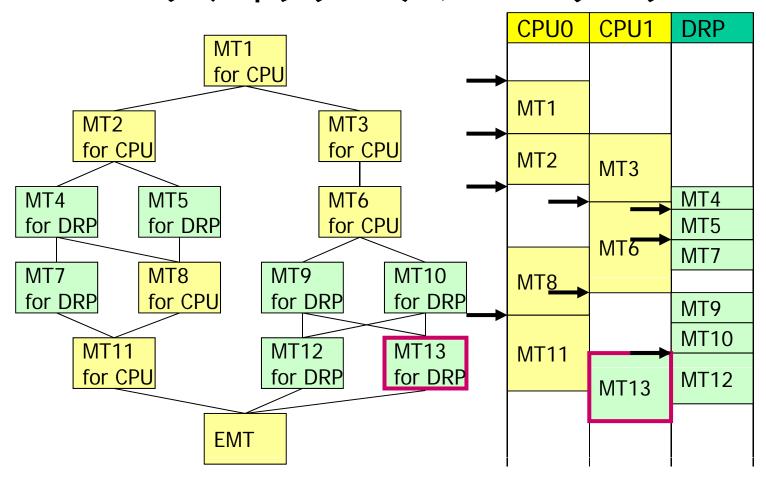

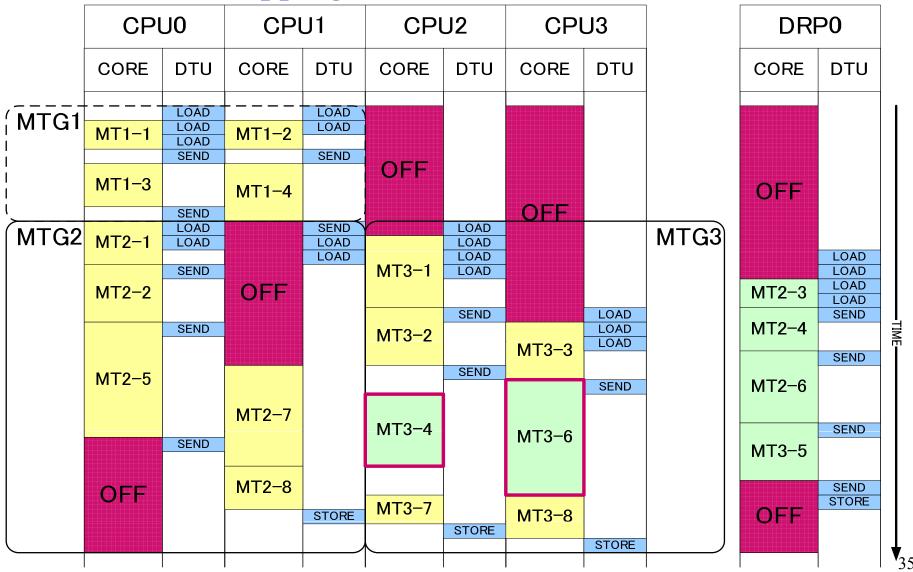

# 粗粒度へテロジニアスタスク並列化 スタティックスケジューリング

# An Image of Static Schedule for Heterogeneous Multi-core with Data Transfer Overlapping and Power Control

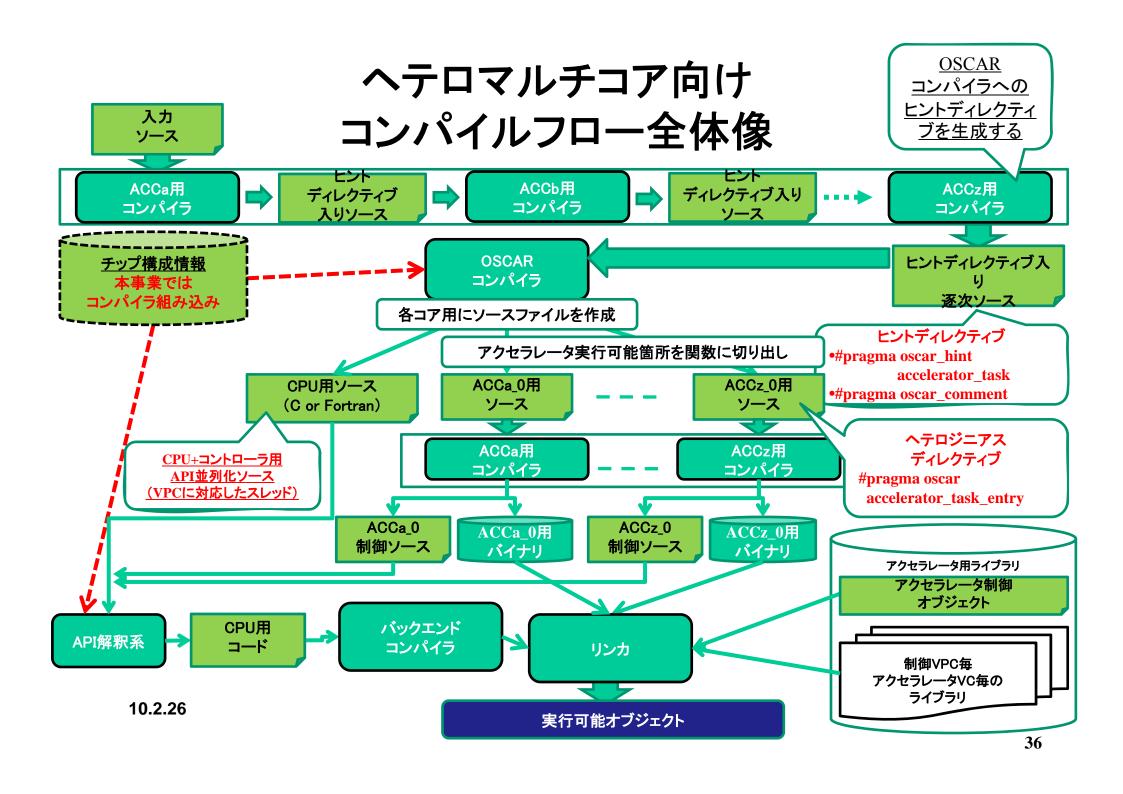

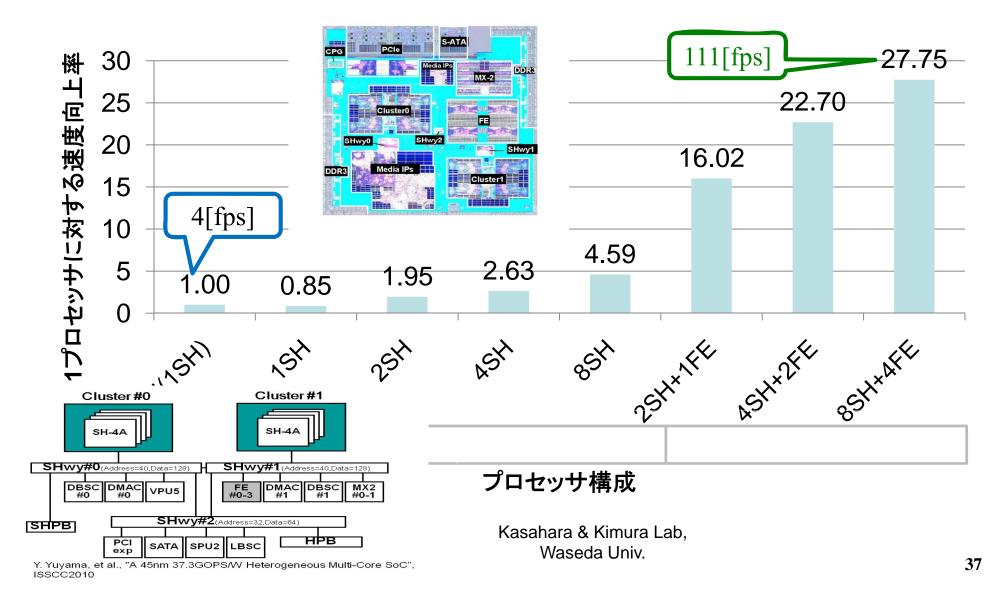

# ヘテロジニアスマルチコアRP-X上での処理性能

NEDO情報家電用へテロジニアスマルチコアプロジェクト(2006-09)

-画像動作追従のためのオプティカルフロー演算のコンパイラ自動並列化(世界初)-

# オプティカルフロー(ライブラリ利用)に対するリアルタイム処理時の消費電力制御

コンパイラ制御なし

コンパイラ制御適用

およそ70[%]の電力削減

平均1.76[W]

平均0.54[W]

Confidential Kasahara & Kimura Lab, Waseda Univ., 2010/07/07

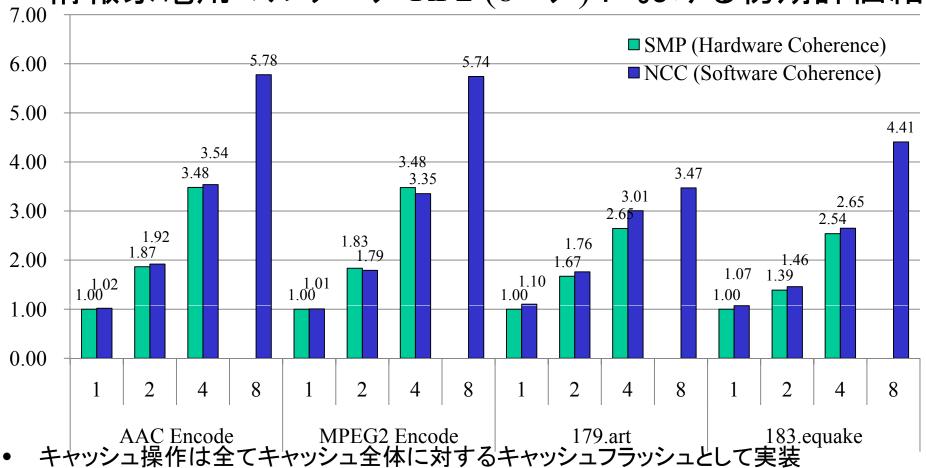

# メニーコアに向けたノンコヒーレントキャッシュ 制御用OSCAR API指示文

- ・新たに5つの指示文を追加

- ・メモリ配置指示文

- noncacheable: 変数をノンキャッシャブルにする

- aligncache:変数の先頭をキャッシュラインの境界にアラインメント

- ・キャッシュ操作指示文

- cache\_writeback:キャッシュ上のダーティラインの書き戻し

- cache\_selfinvalidate:キャッシュラインの無効化

- ・メモリ操作順序保証指示文

- complete\_memop: メモリ操作の完了

# Performance of OSCAR Compiler on IBM p6 595 Power6 (4.2GHz) based 64-core SMP Server

Compile Option:

Sequential: -O5 -bmaxdata:6400000000 -q64 -qarch=pwr6

XLF: -O5 -qsmp=auto -bmaxdata:6400000000 -q64 -qarch=pwr6

-O5 -qsmp=noauto -bmaxdata:6400000000 -q64 -qarch=pwr6 OSCAR:

### メニーコアに向けたソフトウェアキャッシュコヒーレンス制御 評価環境

ルネサス/日立/早大 RP2 (SH-4Aコアを8コア集積)

M. Ito, et al., "An 8640 MIPS SoC with Independent Power-off Control of 8 CPU and 8 RAMS by an Automatic Parallelizing Compiler", ISSCC2008

低コスト化のため5コア以上のハード・コヒーレンシ制御機能無し

→ ソフトウェアによるコヒーレンシ制御が必要

# メニーコアへ向けたソフトウェアコヒーレンス制御の性能

情報家電用マルチコア RP2 (8コア) における初期評価結果

- 部分的なキャッシュ操作を実装することでさらに性能向上が得られる可能性あり

# 平成21年度NEDO「メニーコア・プロセッサ技術 (グリーンITプロジェクト)の先導研究」

低消費電力メニーコアプロセッサ・システム 技術の先導研究

代表研究者 早稲田大学 笠原博徳

早稲田大学、(株)ルネサステクノロジ、富士通(株)、日本電気(株)、(株)東芝

Fujitsu's Vector Manycore Design Evaluated in NEDO Manycore Leading Research, Feb. 2010

各アプリ領域の処理を効率良く実行するための方式 Fuinsu 高並列処理向けクラスタ 高並列処理向けクラスタ L1 cache アクセラレータ ローカル・データ メモリ(LDM) Xbar L1 Xbar L1 専用メモリIF 専用メモリIF On chip On chip Mem. Cont#1 **CSM** CSM Cont#0 動的に 階層型Xbar Xbar L2 → I/O 構成変更 可能 Xbar L1 Xbar L1 専用メモリIF 専用メモリIF L2 Cache L2 Cache Mem. (32MB) Cont#3 (32MB) Cont#2 大容量L2 Cache スルー

Renesas's Low PowerManycore Design Evaluated in NEDO Manycore Leading Research, Feb. 2010

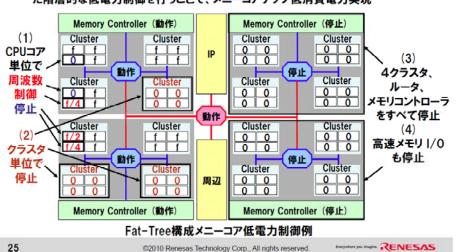

#### 4.3 低電力マルチコア実装技術(1)

◆提案した64コア、Fat-treeアーキテクチャにて、以下のような処理負荷に連動した階層的な低電力制御を行うことで、メニーコアチップ低消費電力実現

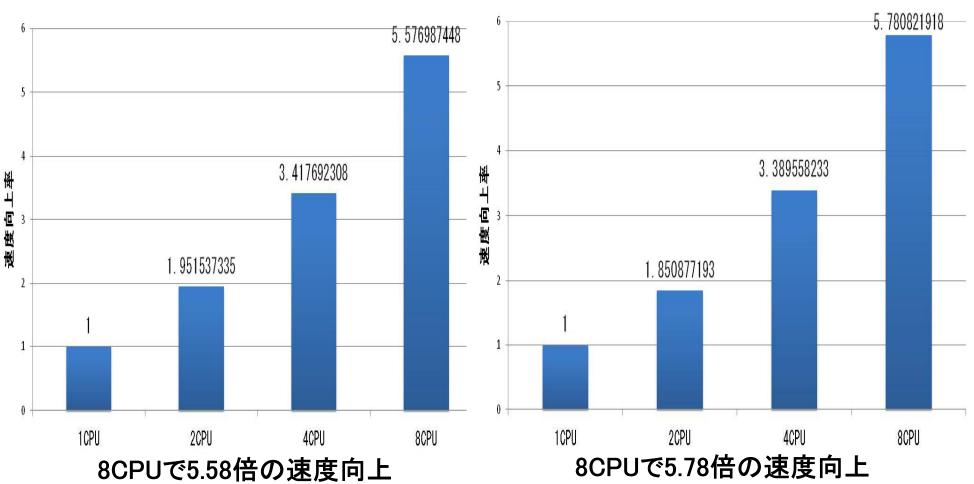

# マルチコアプロセッサ上での 重粒子線ガン治療計画の並列処理性能

Intel Quadcore Xeon 8コアSMP

8CPUで5.78倍の速度同上 IBM Power 7 8コアSMP (日立 SR16000)

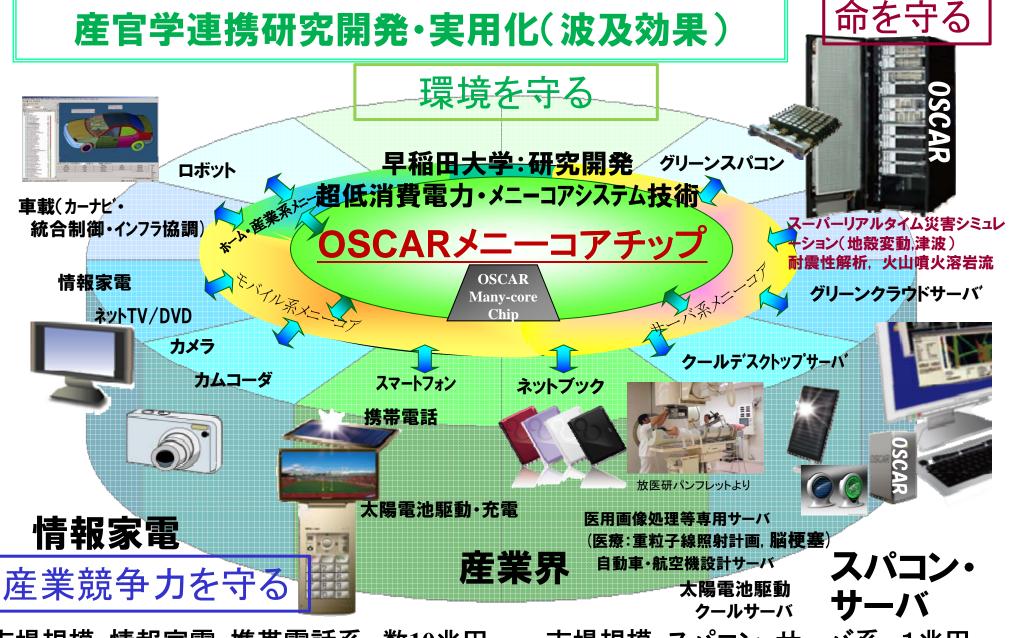

#### グリーン・コンピューティング・システム研究開発センター 概要 2011年4月13日竣工、2011年5月13日開所(記念シンポジウム)

経済産業省「2009年度産業技術研究開発施設整備費補助金」

先端イノベーション拠点整備事業

<目標>

太陽電池で駆動可能で 冷却ファンが不要な 超低消費電力・高性能マルチコア/ メニーコアプロセッサ\*のハードウェア、

\*1チップ上に多数のプロセッサコアを 集積する次世代マルチコアプロセッサ

ソフトウェア、応用技術の研究開発

く産学連携>

日立,富士通,ルネサス,NEC,トヨタ, デンソー,オリンパス,

三菱電機(重粒子線ガン治療)等

<波及効果>

#### 超低消費電力メニーコア

- ▶CO₂排出量削減

- ▶サーバ国際競争力強化

- ▶我が国の産業利益を支える 情報家電,自動車等の高付加価値化

#### 太陽電池駆動・超低消費電力高性能コンピュータの研究開発

#### 研究開発の目的

#### 低炭素・安全安心社会実現への貢献

- ▶太陽電池駆動可能超低消費電力・高性能コンピュータ

- ▶自然冷却(ファン不要)::他国の追従不可な低消費電力

- ▶クラウドサーバ、スパコンの数十MWの電力消費を1/10以下へ削減

- ▶メニーコアを用いたIT機器全体で2025年CO。排出量1000万トン減/年

#### 高度IT機器・自動車産業等の世界競争に勝つ技術の獲得

- ▶ソフトウェア生産性

- ▶従来数ヶ月を要したプログラム並列化を、数分に短縮し生産性向上

- → 情報家電の短製品開発サイクルに対応し低コストで優位化製品を開発

- ▶携帯電話からスパコンまでの高付加価値化(情報家電:数十兆、サーバ:1兆円市場)

- ▶産業利益を支える情報家電、自動車、クラウドサーバ、スパコン等高付加 価値製品を持続的に創出するメニーコアプロセッサシステム技術の開発

#### 研究開発技術

- >太陽電池駆動可能超低消費電力ハードウェア

- ▶メニーコアプロセッサ、太陽電池駆動コンパクトサーバ、 消費電力を1/10以下に抑えるクラウドサーバ・スパコンの試作

- ▶高性能・低消費電力ソフトウェア

- >世界最高性能の自動並列化・世界唯一の自動電力制御機能を実現 したマルチコア用OSCARコンピュータをベースとしたメニーコア及び メニーコアを多数接続したサーバ用コンパイラの試作

- ▶並列プログラム記述標準OSCAR APIの開発

- ▶環境・安全安心・産業競争力強化用アプリケーションソフトウェア

- ▶地球環境シミュレーション、クリーンエネルギー、新デバイス、自動車 設計、航空機設計、医療画像処理、情報家電

#### 研究開発体制

早稲田大学グリーンセンターを中核拠点とし、ハード・ ソフト:日立、富士通、ルネサスエレクトロニクス、NEC、 東芝、アプリケーション:トヨタ、デンソー、オリンパス、三 菱、防災研、地球シミュレーションセンタ、高度情報科学 技術研究機構、JAXA等と産官学連携体制で行う

高付加価値情報家電創出

冷却ファン不要の超低消費 電力メニーコアプロセッサ

**OSCAR** Many-core Chin

太陽電池駆動可 能で医療現場で も使える静音・衛 生的なコンパクト サーバー

を1/10以 下に抑え るグリー ン・クラウ ドサーバ I 、スパコン

消費電力

ソフトの並列 化を数ヶ月 から数分に 短縮する世 界最高性能 自動並列化 コンパイラ

実行時の 電力を 1/4以下 にに抑え る世界初 のソフト 制御技術

高性能デ バイス開発

テラヘルツ発振 超伝導素子

津波伝播シミュレーション

安全安心に向けた地球環境シミュレーション

市場規模:情報家電・携帯電話系 数10兆円

市場規模:スパコン・サーバ系 1兆円

# まとめ

グリーン・コンピューティング・システム研究開発センターでの 産官学連携研究開発(持続的強化のための人材育成含む)

#### 1.環境を守るコンピューティング・システム

太陽光電力等クリーンエネルギーで動作し、自然冷却可能な超低消費電力(マルチコア・メニーコア)プロセッサ・システムのハードウェア・ソフトウェア・応用技術

## 2.命を守るコンピューティング・システム

災害(地震・津波・溶岩流)スーパーリアルタイムシミュレーション技術、医療(重粒子線ガン治療、内視鏡、脳梗塞診断補助)等並列ソフトウェア技術・アーキテクチャ技術

## 3.産業競争力を守るコンピューティング・システム

我が国の主要産業である自動車、情報家電、ロボット等の安全、安心、快適、省エネ、高機能、高生産性を実現し高付加価値化に貢献するソフトウェア・ハードウェア・API技術