## 組込みマルチコア 最先端並列化コンパイラ技術

## 早稲田大学

理工学術院 基幹理工学部 情報理工学科 アドバンストチップマルチプロセッサ研究所 所長 教授 笠原博徳

http://www.kasahara.cs.waseda.ac.jp/

## 目次

- 1. マルチコアEverywhere

- 情報家電,PCからスパコンまで 至る所にマルチコア

- 命令レベル並列の限界

- メモリウォール問題への対応

- 消費電力削減の必要性

- ソフトウェア生産性がポイント

- コンパイラ協調型マルチコアの必要性

- 2. 情報家電マルチコアプロジェクト

- NEDO コンパイラ、マルチコア プロジェクト

- ・ 我が国の並列化コンパイラ競争力

- コンパイラ競争力を生かしたマルチ コアアーキテクチャ開発

- 組込用マルチコアAPIの策定

- 3. マルチコア用コンパイラ技術

- マルチグレイン並列化

- データローカライゼーション

- DMAによるデータ転送オーバーラップ

- 周波数•電圧•電源遮断制御

- 市販コンパイラとの性能比較

- 4.組込用マルチコア上での API を用いた自動並列化性能

- OSCAR型メモリアーキテクチャ

- ・ メモリ管理、DMA、電力制御API

- 試作OSCAR型4及び8コアチップ・ RP1・2、既存FR1000チップ上での APIを用いた自動並列化性能

- 5. ヘテロジニアスマルチコア

- 6. まとめ

## マルチコアEverywhereの時代

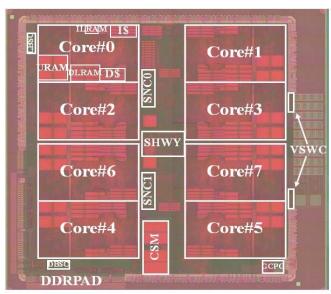

NEDOリアルタイム情報家電用マルチコアプロジェクトルネサス試作チップ(OSCAR)標準アーキテクチャ IBM BlueGene/L

Lawrence Livermore National Laboratory2005/

1プロセッサチップ上に2プロセッサ集積

- ◆ 組み込みプロセッサからスパコンまで

- ▶情報家電用マルチコア

カーナビ,携帯電話,ゲーム,デジタルTV, DVD IBM/ Sony/ Toshiba Cell, Fuijtsu FR1000, NEC/ARMMPCore&MP211, Panasonic Uniphier, Renesas SH multi-core(4 core RP1, 8 core RP2) Tilera Tile64, SPI Storm-1(16 VLIW cores)

>PC,サーバ

Intel Quad Xeon, Core 2 Quad, Montvale, Tukwila, 80 core, AMD Quad Core Opteron, Phenom

➤ WSs, Deskside & Highend Servers

IBM Power4,5,5+,6, HPCS 10PFLOP(Power7)

Sun Niagara(SparcT1,T2), Rock

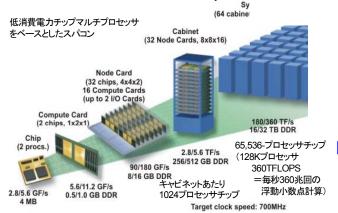

▶スーパーコンピュータ

地球シミュレータ, 2002年3月完成, 5120ベクトルプロセッサ : 40TFLOPS

IBM Blue Gene/L: 360TFLOPS, 2005,低消費電力マルチコアベース128K processor chips, BG/P 2008 1PFLOPS(2008), BG/Q 10PFLOPS (2011)

- アプリケーションソフトの充実,短期間システム開発,低コスト, 低消費電力, 高機能化が市場競争力決定 <例>携帯電話,ゲーム,自動車

- 自動並列化コンパイラ協調型マルチコアプロセッサ必要

## リアルタイム情報家電が市場を牽引

- ・ 市場規模は国内で3兆円、全世界で10兆円を超える

- ・ 2010年に100兆円規模市場へ成長

|                 | '03  | '07  | 年平均<br>成長率 % |

|-----------------|------|------|--------------|

| デジタルスチルカメラ(M台)  | 49   | 76   | 12           |

| デジタルTV(M台)      | 6    | 27   | 45           |

| DVDレコーダ(M台)     | 3.6  | 33   | 74           |

| PC用DVD(記録型)(M台) | 27   | 114  | 43           |

| 携帯電話(M台)        | 490  | 670  | 8            |

| 自動車用半導体需要(B\$)  | 14.0 | 20.9 | 11           |

「電子・情報技術分野の技術ロードマップ」 独立行政法人新エネルギー・産業技術総合開発機構 2005年4月より

## 早稲田でのマルチコアハード・ソフト研究

自動並列化コンパイラ協調型 チップマルチプロセッサ (マルチコアプロセッサ)

OSCAR: Optimally Scheduled

Advanced Multiprocessor

- ▶ 携帯電話・DVD・ゲーム・カーナビ・デジタルTV等の情報家電

- > 次世代スーパーコンピュータ

### 産官学連携

STARC (11社出資 半導体理工学研究センター) 2000-2004:基礎研究 2004-2006:実用化研究 (富士通,東芝,NEC,ソニー,松下等)

2001-2005: STARC寄附講座SoC設計技術

### 経産省/NEDO

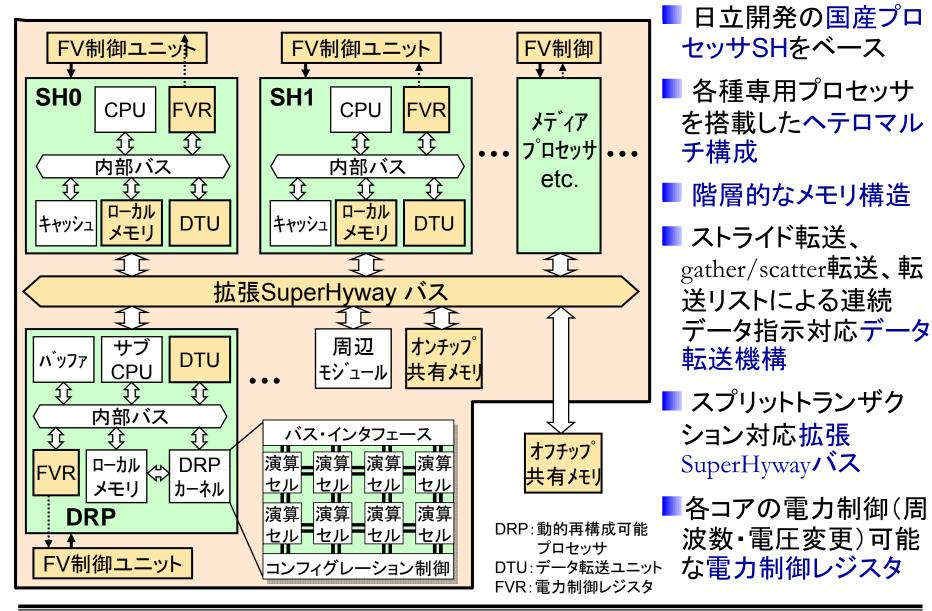

2004-2006: 「大学発事業創出実用化研究開発事業」 先進へテロジニアス・マルチプロセッサ(日立) 2005-2007: リアルタイム情報家電用マルチコア (日立,ルネサス,富士通研,東芝,松下,NEC)

2006-2009:情報家電用へテロジニアスマルチコア (日立,ルネサス,東工大) 経済産業省/NEDOリアルタイム情報家 電用マルチコア(2005.7~

2008.3)\*\*

### <u>新マルチコア</u> プロセッサ

- •高性能

- •低消費電力

- •短HW/SW開 発期間

- •各チップ間でア プリケーション 共用可

- •高信頼性

- •半導体集積度と共に性能向上

### 開発マルチコアチップは情報家電へ

\*\*日立,富士通,ルネサス,東芝,松下,NEC

### NEDOリアルタイム情報家電用マルチコアチップ・デモの様子

### 第74回総合科学技術会議【平成20年4月10日】

第74回総合科学技術会議の様子(1)

第74回総合科学技術会議の様子(3)

第74回総合科学技術会議の様子(2)

第74回総合科学技術会議の様子(4)

### 最近の科学技術の動向

情報爆発時代に向けた省エネルギー技術

平成20年4月10日 総合科学技術会議

### 3. 我が国がリードする次世代IT省エネ技術

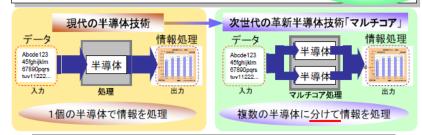

● 半導体の消費電力を、一気に数分の1にする革新技術: マルチコア技術

ソフトウェア技術と連携し、① 処理の自動最適割り振り、② 電力制御 により、 大幅な省電力化を実現 ➡ 将来の国際競争力の原動力に

マルチコアの最新型:8個の半導体(コア) 消費電力

#### 2. 消費電力削減に向けた技術的アプローチ

情報爆発時代に向け、革新技術により抜本的に省エネ。

#### I Tによる社会の省エネ I T機器の省エネ (ネットワーク機器、サーバ、記憶装置、PC、表示装置) ■日本が得意とする、センサー、無線等を ■コンピュータ:半導体の微細化技術 活用し、工場、ビル、住宅の熱・照明・暖房 等のエネルギー消費を最適に自動制御。 2011年までに消費電力 25%減 <例:ビル空調の最適制御技術> ■表示装置:発光効率向上 2012年までに消費電力 25%減 ■電力制御素子:直流/交流変換 に半導体を利用 2009年までに消費電力 70%減 半導体をさらに省エネにする技術 高層ビルの空調用ポンプの消費電力 (マルチコア) を、最大で90%削減(実績) 消費電力 ITによる最適制御のみによる削減。 80%以上 減

#### 「マルチコア技術」の今後の課題

・空調全体の消費エネルギーは約5%削減

- ソフトウェア技術の高度化 自動最適割り振りソフトウェア

- 設計技術の開発 複雑化する設計技術への対応

あらゆる製品にも普及

これらを駆動・制御する 「マイコン」においては、 日本が世界シェアの約50%

### 4. ITの革新的省エネに向けた取組

我が国がリーダーシップを示し、国際連携の下、開発・普及を加速。 我が国のITの競争力強化も図る(グリーンIT)。

#### 政府による革新的技術開発の支援

■ グリーンITプロジェクト: 08年度新規、2025年までにIT機器の省エネ効率を50%向上

#### 省エネ技術・製品の普及、国際展開

- 省エネ法トップランナー制度:業務部門(ルータ等IT機器)の強化

- 産学官連携協議会(グリーンIT推進協議会)と海外組織の国際連携・展開

グリーンIT推進協議会 133のIT企業、関連団体および IT利用者により2月設立

環境貢献の評価方法 技術ロードマップ

海外組織 100程のIT企業等により 設立されたコンソーシアム等

環境 調和型 [ T社会 の構築

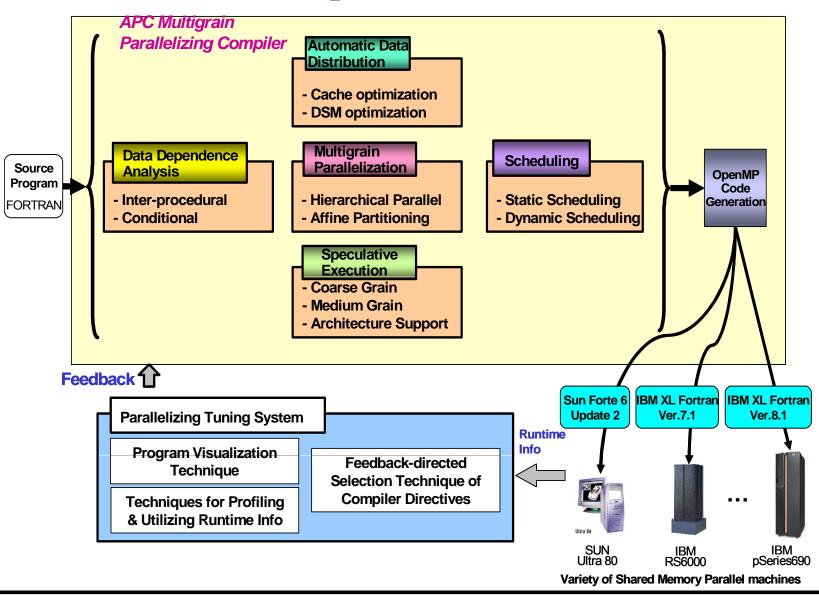

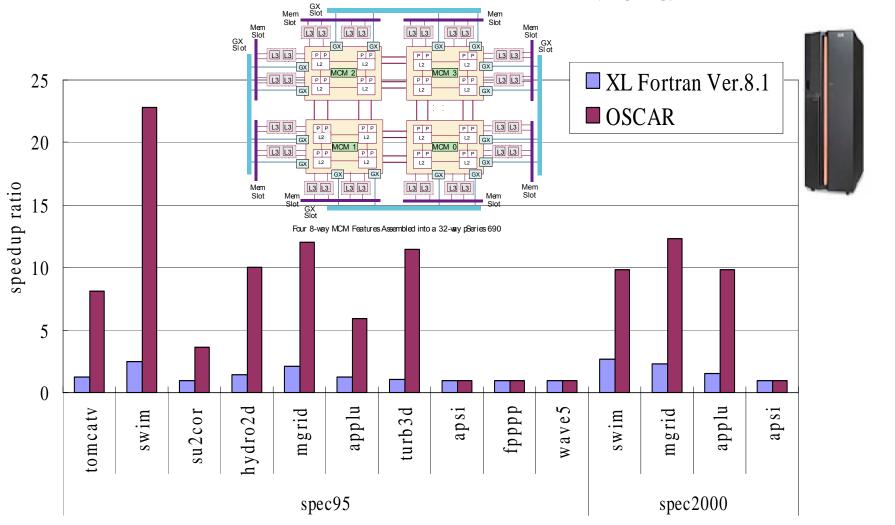

### ミレニアムプロジェクトIT21 経済産業省/NEDO「アドバンスト並列化コンパイラ」

### 概要

- <リーダ> 早大 笠原博徳

- <研究期間> 2000.9.8 -2003.3.31

- <連携機関> 早大、日立、富士通、 産総研、日本情報処理開発協会等

- <目標>国内産業界の基幹ソフト ウェア(並列化コンパイラ)技術 を、世界のトップに押し上げる。

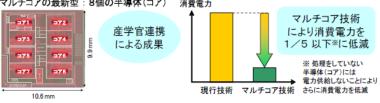

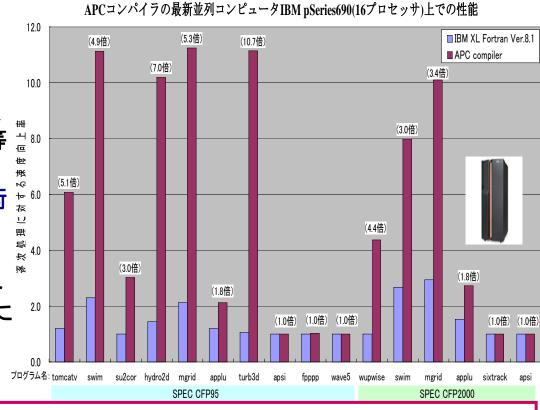

- <結果> IBM最新高性能サーバ pSeries690 16プロセッサ上で世界 標準科学技術計算ベンチマーク に対し、IBM最新コンパイラXL

Fortran Ver.8.1に比べ平均3.5倍、 最大10.7倍の高速化に成功。

APCコンパイラの性能: 各計算の速度向上率を表す2本バーの内、 左(青)はIBMコンパイラ、右(赤)はAPCコンパイラによる性能。

### 評価

- <世界からの評価> Stanford Univ. Univ. of Illinois, Purdue Univ. École des Mines de Paris APCプロジェクトにより、高性能コンピュータ用のソフトウェアで日本が世界一。

- <内閣府IT21評価助言会議>平成15年7月18日(評価抜粋)「米国のこの分野のキーパースンからも評価されており、米国を凌駕する並列コンパイラ技術を構築した」

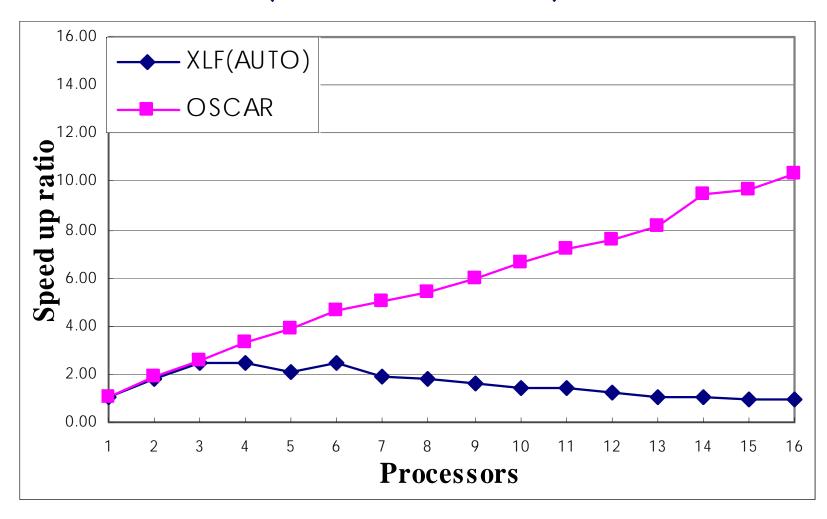

## OSCARマルチグレイン並列化コンパイラのIBM pSeries690 ハイエンドサーバ上での性能 (SPEC95 102.swim)

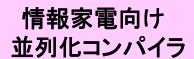

### マルチコア用コンパイラ技術

プロセッサ高速化における3大技術課題の解消

1. 半導体集積度向上に対する速度向上の鈍化 マルチグレイン並列化

ループ並列化だけでなく、粗粒度タスク並列 化を含めた複数粒度の並列性をプログラム全 域のより抽出し速度向上

2. メモリウォール問題

ローカルメモリ及びデータ転送最適化 ローカルメモリ、キャッシュへのデータ分割配 置、タスク実行とオーバーラップしたデータ転送によりオーバーヘッド最小化 → API策定

3. 消費電力増大による速度向上の鈍化

コンパイラ低消費電力制御

アプリケーション内でのきめ細かい周波数・ 電圧制御・電源遮断により消費電力低減 > API策定

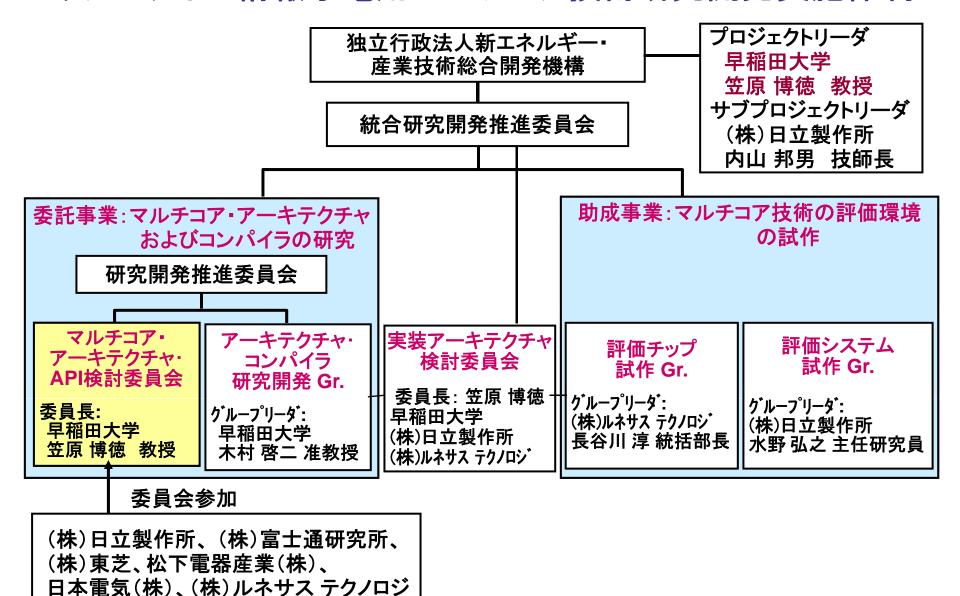

# 経済産業省・NEDO半導体アプリケーションチップリアルタイム情報家電用マルチコアプロジェクト

- ■目的 DVD、デジタルTV、カーナビ、携帯電話等リアルタイム情報家電における 優位化製品創出を目指したプロセッサ技術の国際競争力強化

- ■自然冷却を前提とした3W程度以下の消費電力のマルチコアプロセッサを研究開発

- ■ロボット、自動車等にも適用できる組込リアルタイム処理(デッドラインを持った処理)にも適用できる使いやすいマルチコアプロセッサを研究開発

- ■研究期間 平成17年7月~平成20年3月

- ■内容 下記特徴をもつマルチコア・アーキテクチャ及びコンパイラ技術の確立

- ■優れた価格性能

- ■短ハードウェア・ソフトウェア開発期間

- ■低消費電力

- ■同一アーキテクチャでローエンドからハイエンド製品まで柔軟に対応

- ■集積度向上に対するスケーラブルな性能向上

- ■異なる企業開発のマルチコア間でのアプリケーションの共用

## リアルタイム情報家電用マルチコア技術研究開発実施体制

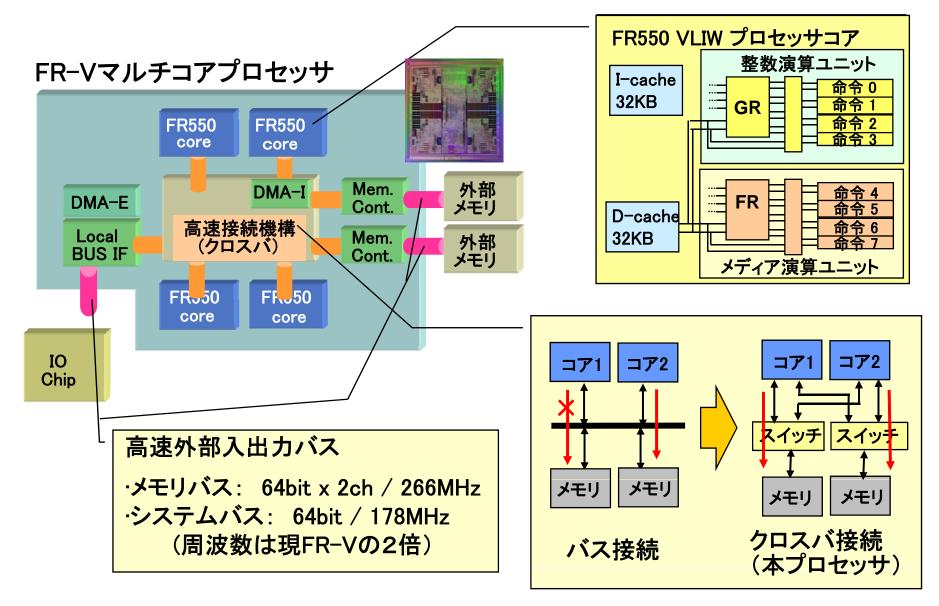

## 富士通研FR-Vマルチコアプロセッサ

## NEC携帯電話向けアプリケーションプロセッサ: MP211

快適なインターネット・アクセス環境をモバイル機器で

### ねらい

デジタル放送、高性能ダウンロードアプリなどを携帯電話で実現 するための高速低電力アプリケーションプロセッサ

### 成果/革新性

- オンチップ並列処理(タスク並列型)

ARM926(200MHz)×3, DSP(200MHz),

Graphics Engine, Image Processor,

Security Engine

- ・マルチコア仮想化ソフトウェア

- 高性能バスアーキテクチャ

- ・電源制御による低電力化

- デジタル放送のようなリアルタイム 処理をCPU分離し、性能確保

- ・ダウンロードアプリをCPU分離 することによるセキュリティ確保

MP211('04発表) -130nm -8.9mm角

ネットワーク サービス

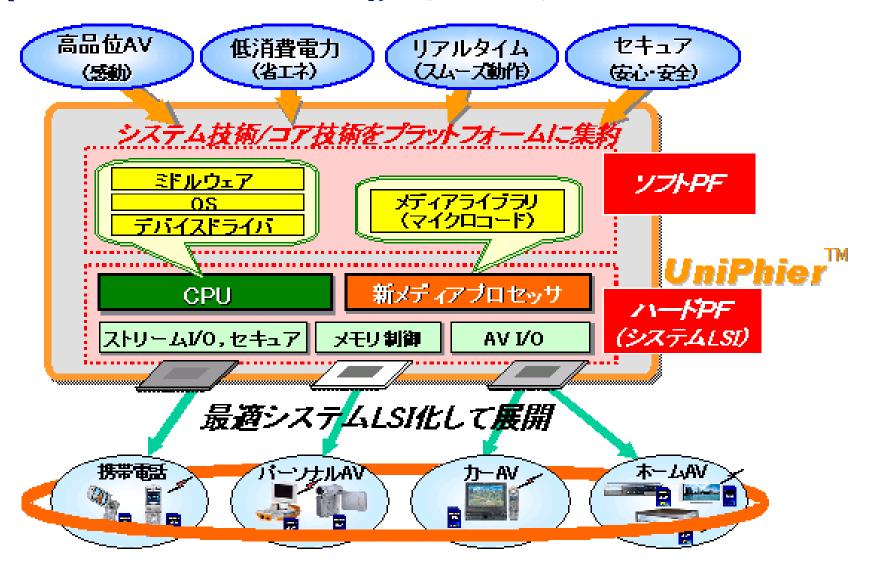

## 松下UniPhier統合プラットフォーム

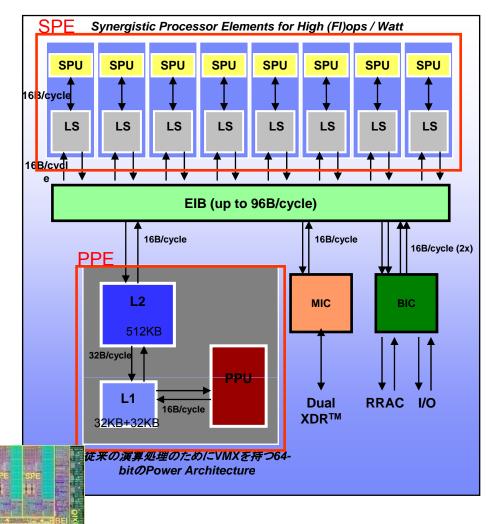

## ソニーIBM東芝CELLプロセッサ概要

- Power Processor Element (PPE)

- PowerコアはOS及び制御集中 タスクを処理

- 2-wayマルチスレッド

- Synergistic Processor Element (SPE)

- 8つのSPE が優位な演算性能を 提供

- Dual issue のRISCアーキテク チャ

- 128bit のSIMD型(16 wayまで)

- 128 x 128bit General Registers

- 256KB Local Store

- 専用DMA engines

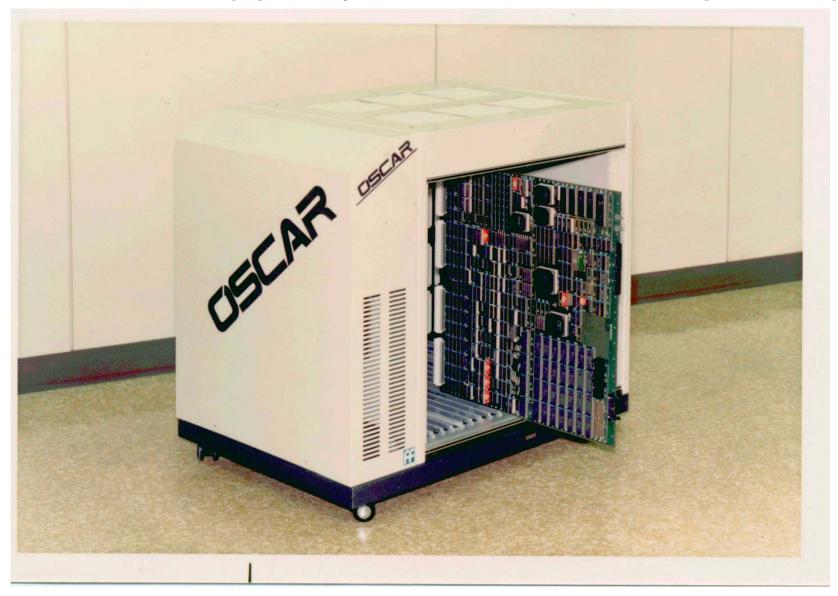

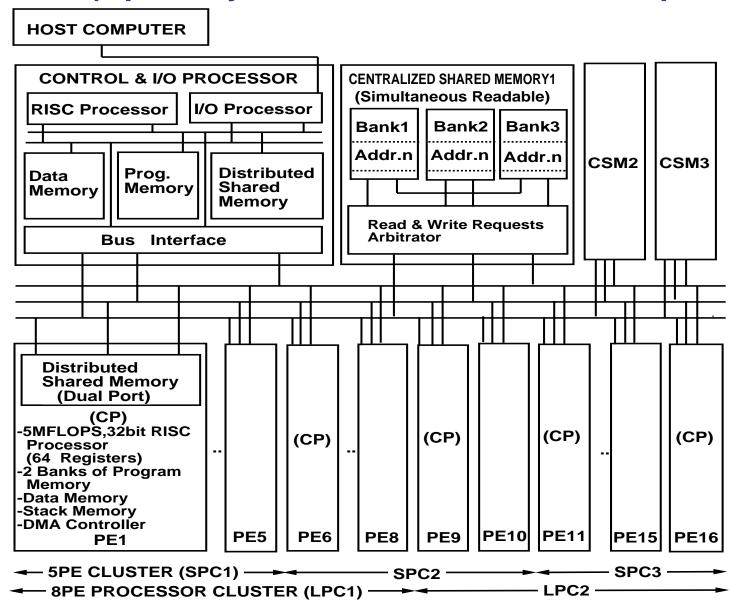

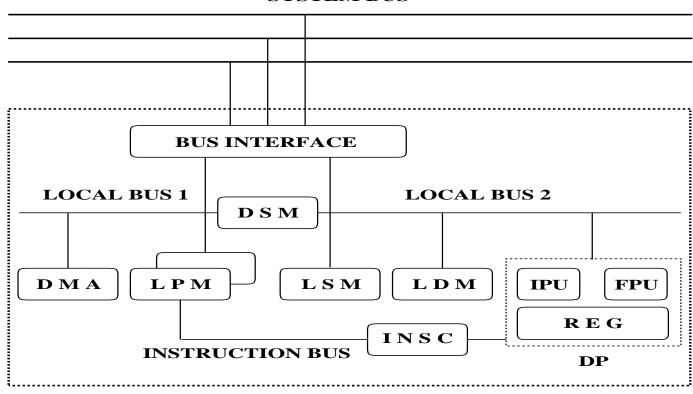

### 1987年 OSCAR(Optimally Scheduled Advanced Multiprocessor)

### OSCAR(Optimally Scheduled Advanced Multiprocessor)

## **OSCAR PE (Processor Element)**

**DMA: DMA CONTROLLER**

: LOCAL PROGRAM MEMORY

(128KW \* 2BANK)

INSC: INSTRUCTION

**CONTROL UNIT**

: DISTRIBUTED

**SHARED MEMORY (2KW)**

: LOCAL LSM

STACK MEMORY (4KW)

I DM: LOCAL DATA MEMORY

(256KW)

: DATA PATH

IPU : INTEGER

PROCESSING UNIT

FPU: FLOATING

PROCESSING UNIT

REG: REGISTER FILE

(64 REGISTERS)

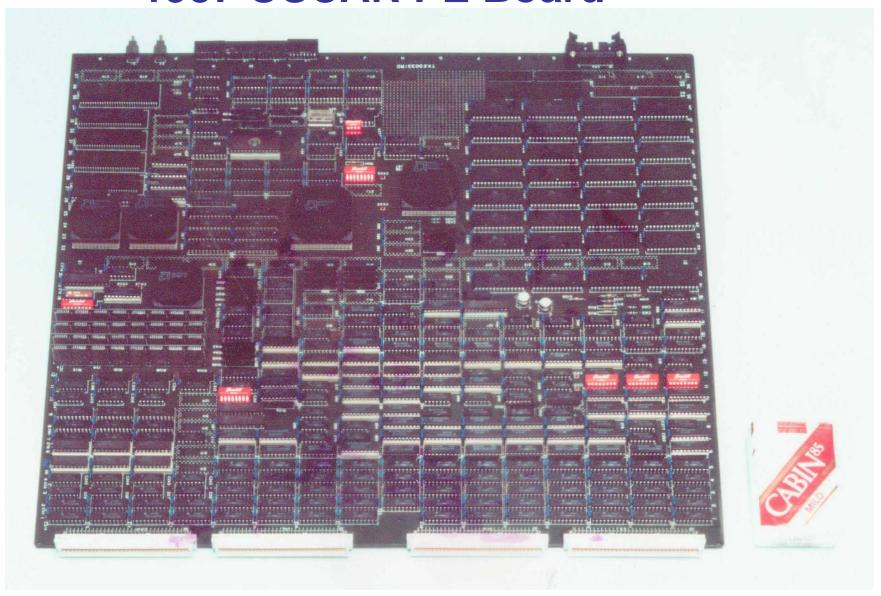

## 1987 OSCAR PE Board

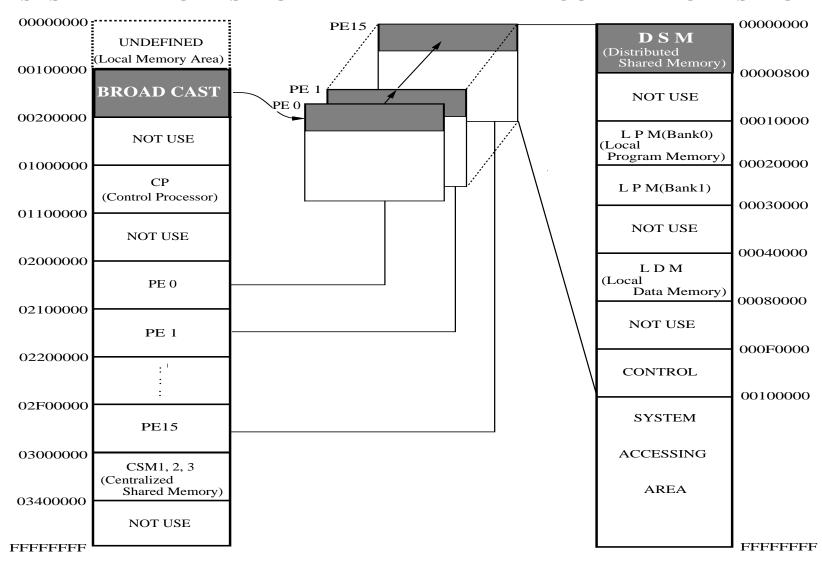

## **OSCAR Memory Space**

#### SYSTEM MEMORY SPACE

#### LOCAL MEMORY SPACE

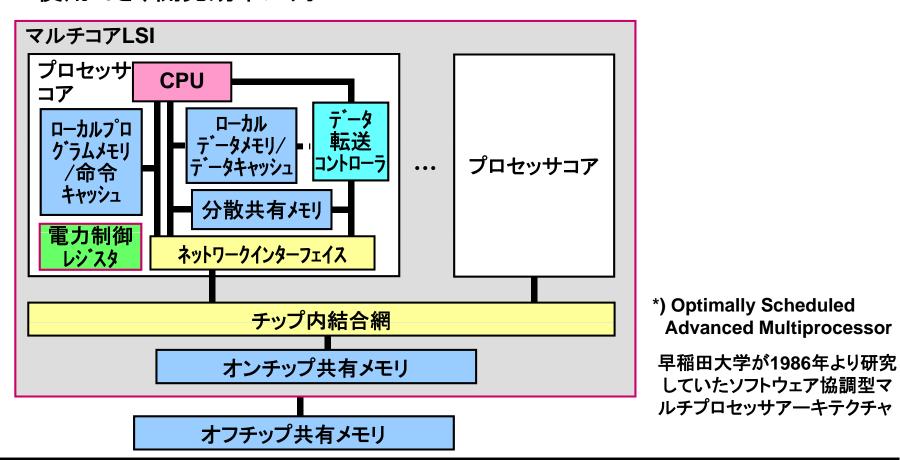

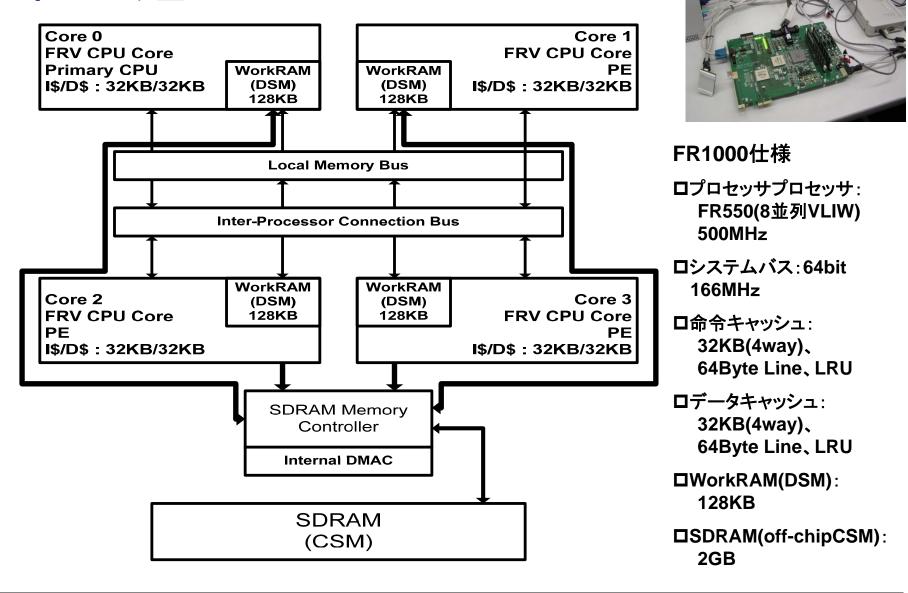

## NEDOリアルタイム情報家電用マルチコアプロジェクトにて 策定したマルチコア・アーキテクチャ

- ・ 6社の協力を得て、OSCAR\*アーキテクチャをベースにメモリ構成や消費 電力制御を定義

- ・ 策定アーキテクチャに準拠するマルチコアLSI間では共通のコンパイラを 使用でき、開発効率が向上

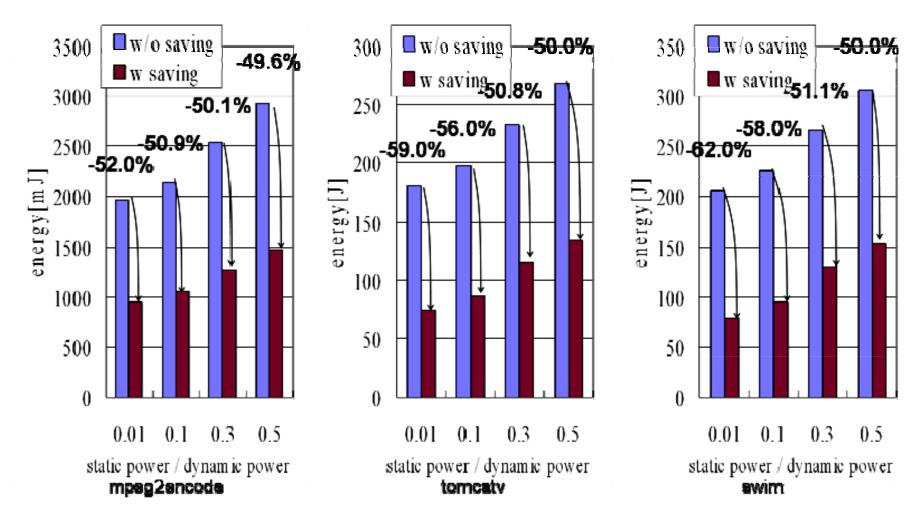

## APIを用いたコンパイル・実行の流れ

### API詳細は下記にて公開

http://www.kasahara.cs.waseda.ac.jp/

情報家電アプリケー ションプログラム (逐次型プログラム)

- ●プログラム全域から 並列性を抽出

- ●データ配置の最適化

- ●データ転送オーバー ヘッドの最小化

- ●消費電力の最小化

**API: Application Programming Interface**

情報家電用 マルチコア 並列化 API

策定した指示文により、タスク制御・ データ転送・電力制御を指示

各社チップ用 並列マシン コードに変換

情報家電用 並列化API プログラム

Proc0

指示文 並列処理 部分

Proc1

指示文 並列処理 部分

API 既存コン 解釈部 パイラ

コード生成コンパイラ

コード生成コンパイラ

API ベースコ 解釈部 ンパイラ

> コンパイラ協調型 低消費電力 高性能マルチ コアチップ

実行

A社 チップ

実行 コード 各社チップを利用可

能

マルチコア LSI

本アーキテクチャに準拠するマルチコアLSI間では 策定APIを利用することにより、共通のコンパイラが 利用でき、ソフト開発効率が向上

## リアルタイム情報家電用マルチコア用API

- ・策定マルチコア・アーキテクチャおよび、このアーキテクチャにおける並列化プログラムの動作やデータ配置・転送を指示する標準的なAPIとして、 共有メモリ型並列プログラミングの標準 APIであるOpenMP 互換のスレッド生成・同期・排他制御・変数属性に加え、6 社と共同で以下を策定

- ・ メモリ配置指示 (小容量メモリ上での高速実行を可能とする)

- ローカルメモリ・分散共有メモリ・オンチップ共有メモリへの変数の配置を指定

- ・データ転送指示 (プロセッサ間データ転送オーバーヘッド最小化)

- 高機能DMAコントローラを利用し、メモリ間のデータ転送やプロセッサ動作とオーバラップした転送を指示

- · 電力制御指示 (低消費電力化)

- 各プロセッサコアの動作周波数・電圧、電源遮断制御を指示: 策定中

- ・ ヘテロジニアスマルチコア指示 (アクセラレータ混載LSI対応)

- 汎用プロセッサと専用プロセッサでの処理分担を指示: 策定中じょうほう

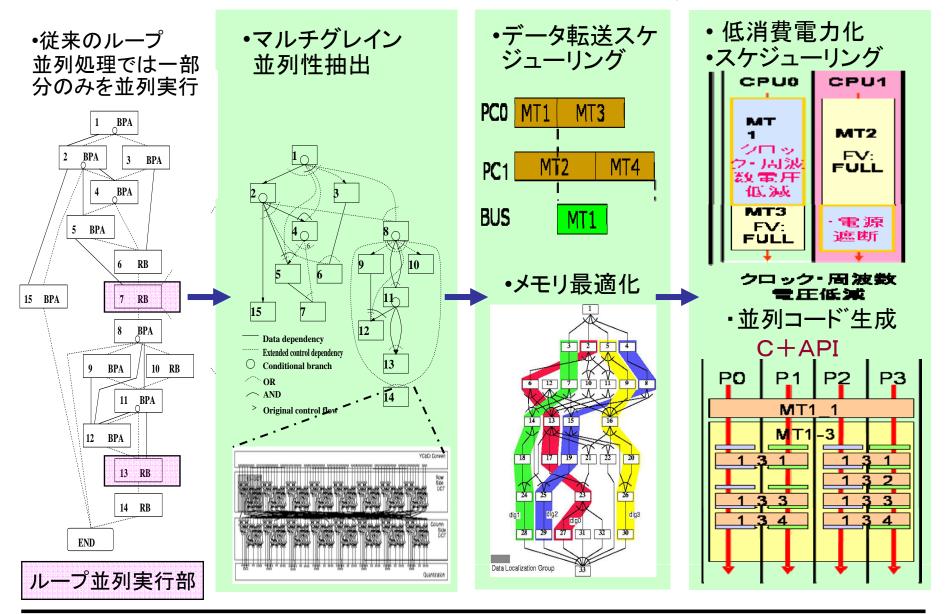

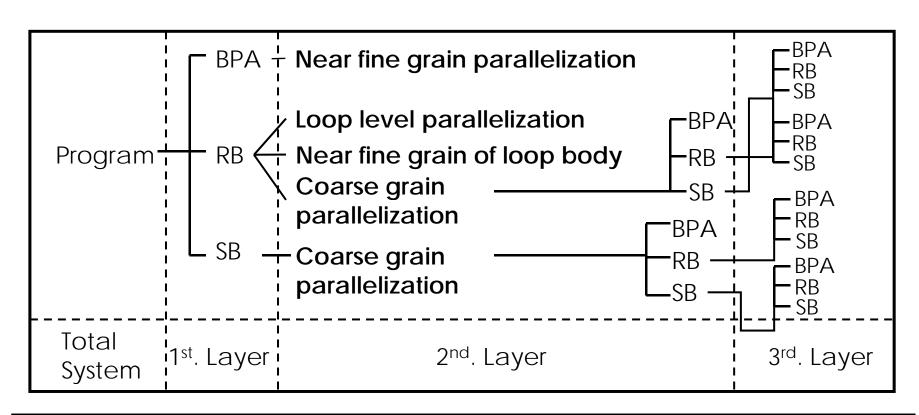

## OSCARマルチグレイン並列化

## 粗粒度タスクの生成

## ■マクロタスク (MTs)

- ä Block of Pseudo Assignments (BPA): Basic Block (BB)

- ä Repetition Block (RB): natural loop

- ä Subroutine Block (SB): subroutine

## 粗粒度タスク間の並列性抽出 最早実行開始条件解析

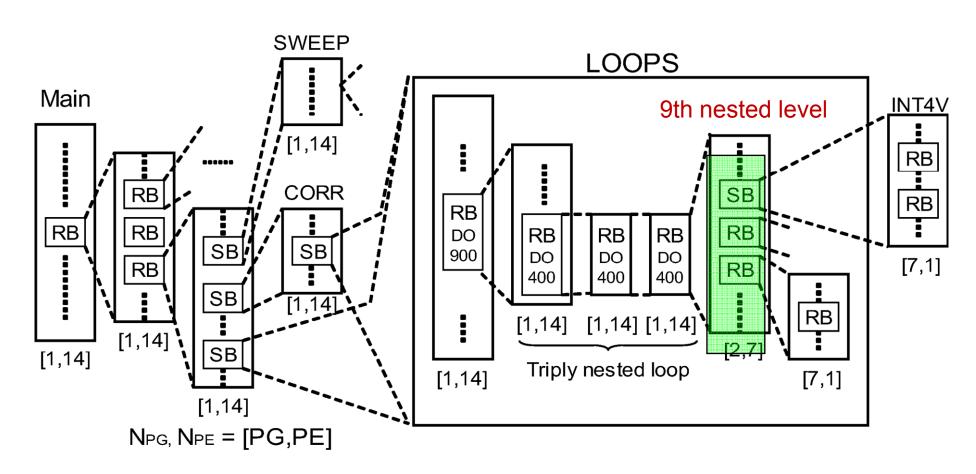

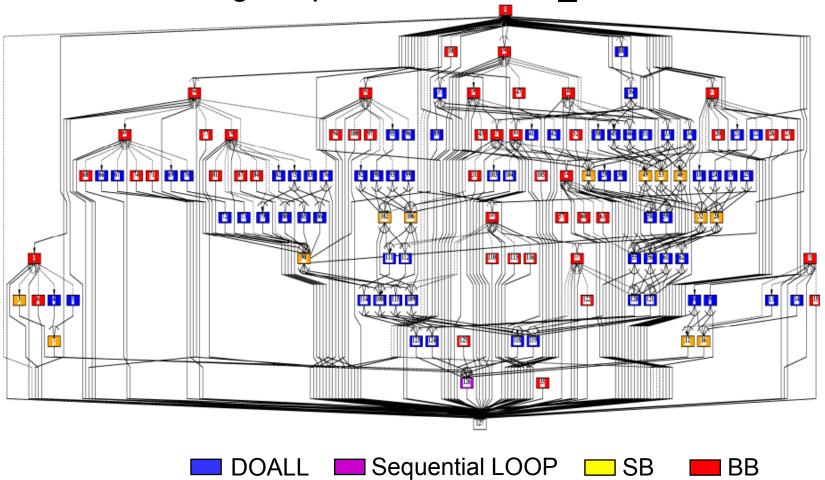

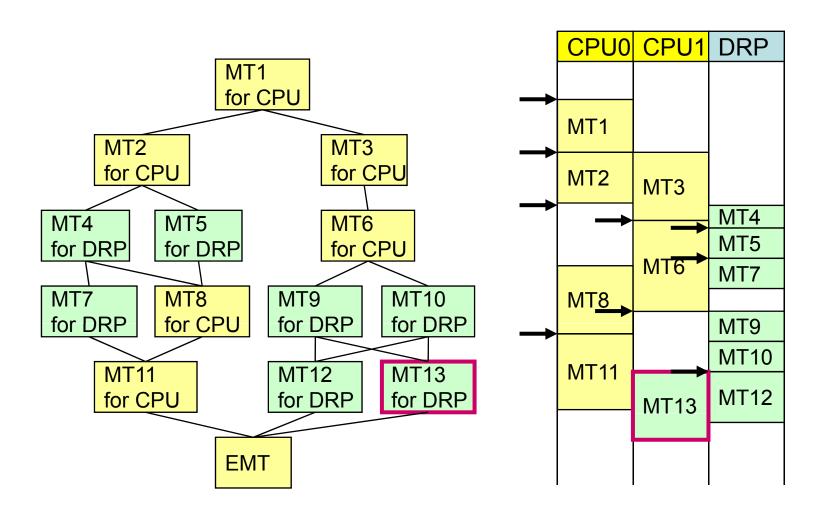

## 階層的な並列性抽出 (su2corプログラムの例)

- Using 14 processors

- Coarse grain parallelization within DO400 of subroutine LOOPS

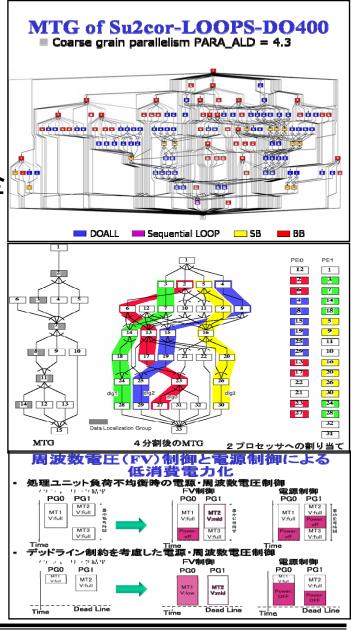

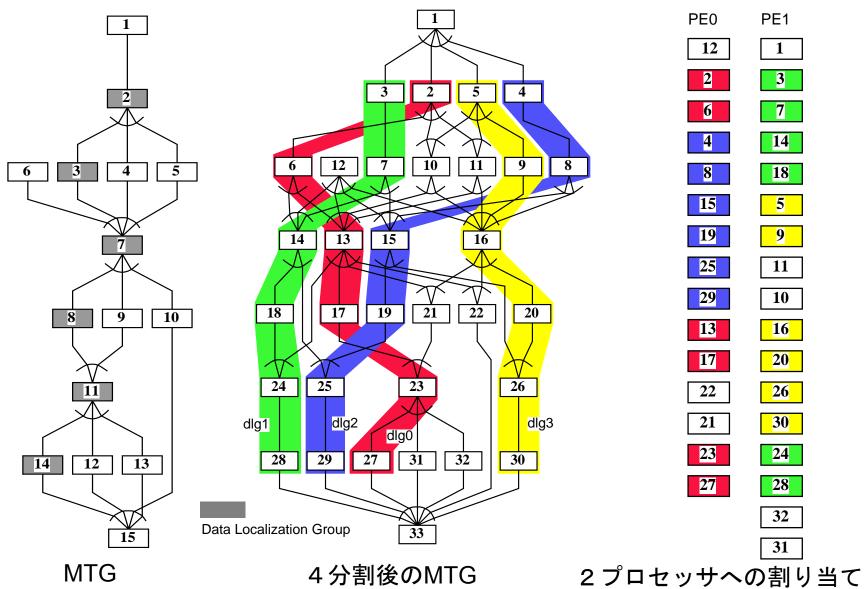

## MTG の例(Su2cor-LOOPS-DO400)

Coarse grain parallelism PARA\_ALD = 4.3

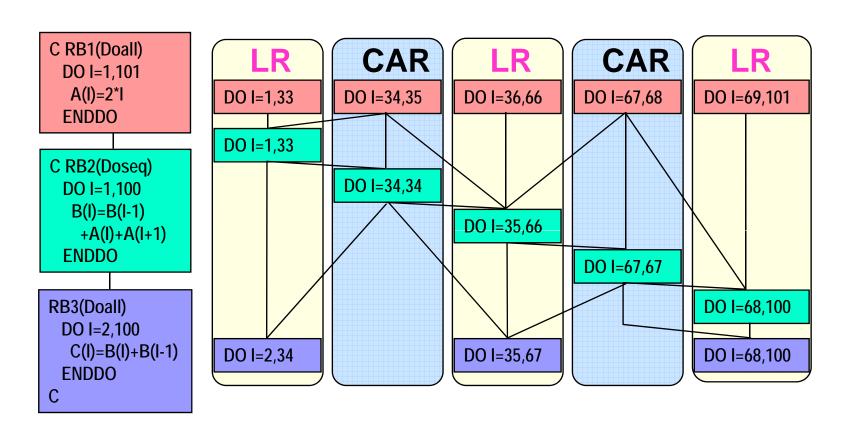

## データローカライゼーション:ループ整合分割

- Decompose multiple loop (Doall and Seq) into CARs and LRs considering inter-loop data dependence.

- Most data in LR can be passed through LM.

- LR: Localizable Region, CAR: Commonly Accessed Region

## データローカライゼーションのイメージ

### データローカライゼーションの例 Spec95 Swim

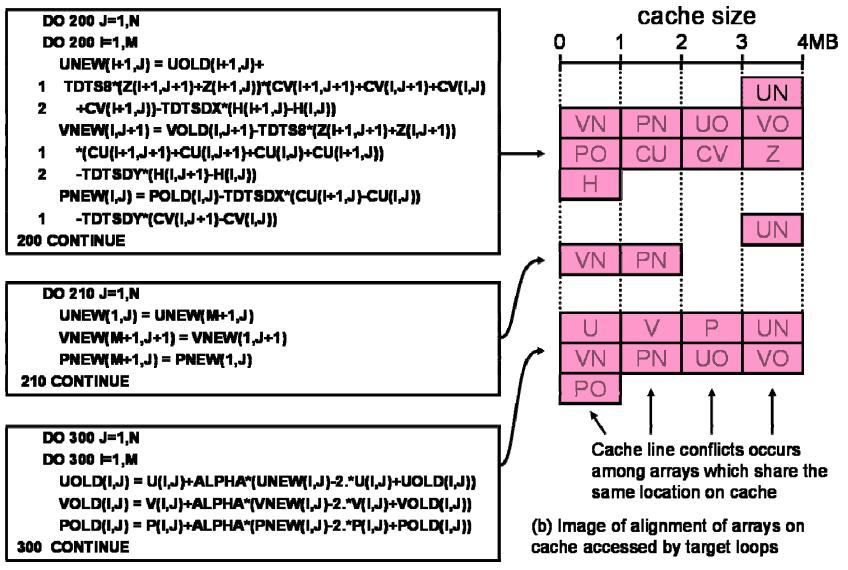

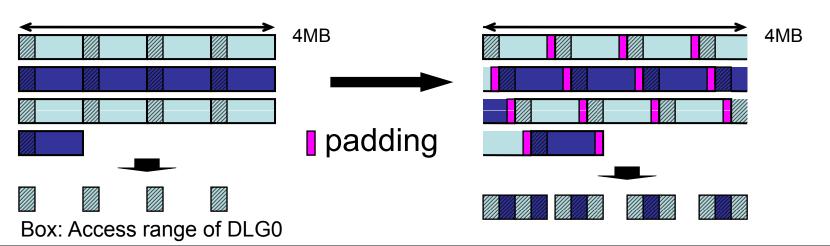

## 配列パディングを用いたキャッシュラインコンフリクト軽減 のためのデータレイアウト変更

Declaration part of arrays in spec95 swim

### before padding

after padding

PARAMETER (N1=513, N2=513)

PARAMETER (N1=513, N2=<u>544</u>)

COMMON U(N1,N2), V(N1,N2), P(N1,N2),

- \* UNEW(N1,N2), VNEW(N1,N2),

- 1 PNEW(N1,N2), UOLD(N1,N2),

- \* VOLD(N1,N2), POLD(N1,N2),

- 2 CU(N1,N2), CV(N1,N2),

- \* Z(N1,N2), H(N1,N2)

COMMON U(N1,N2), V(N1,N2), P(N1,N2),

- \* UNEW(N1,N2), VNEW(N1,N2),

- 1 PNEW(N1,N2), UOLD(N1,N2),

- \* VOLD(N1,N2), POLD(N1,N2),

- 2 CU(N1,N2), CV(N1,N2),

- \* Z(N1,N2), H(N1,N2)

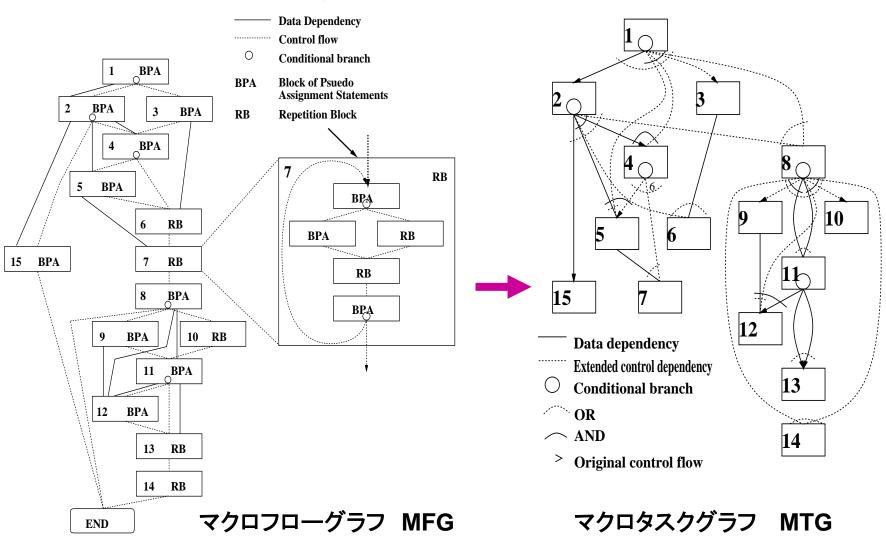

# 共有メモリマルチプロセッサ用API(OprnMP)を用いたAPC OSCAR Compiler (各社のマルチプロセッサで使用可)

### Centralized 策定マルチコアAPIOpenMPを用いた scheduling 粗粒度タスク並列化コードのイメージ code **SECTIONS** 1st layer **SECTION SECTION** T3 T4 T5 T6 Distributed MT1 1 scheduling MT1 1 code MT1 2 SYNC RECV DOALI MT1 3 SB MT1 4 1\_3\_1 RB 1 3 1 1 3 4 **END SECTIONS** 2nd layer Thread **Thread** 3rd layer group1 group0

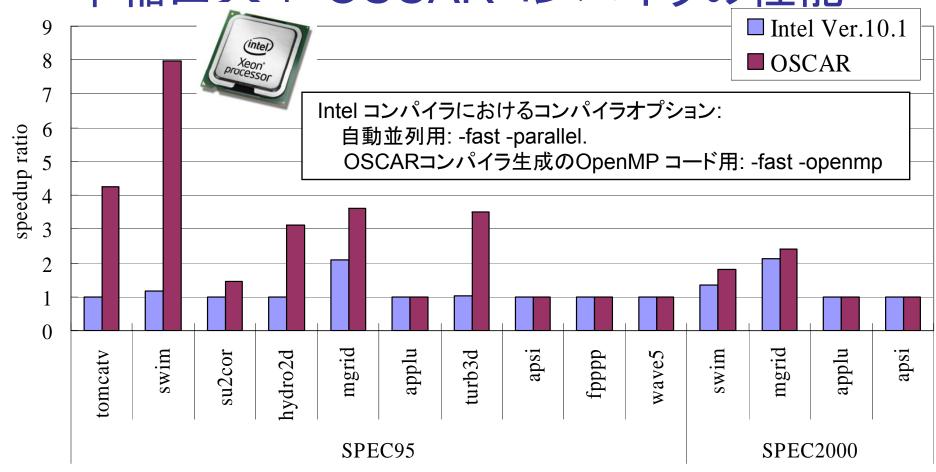

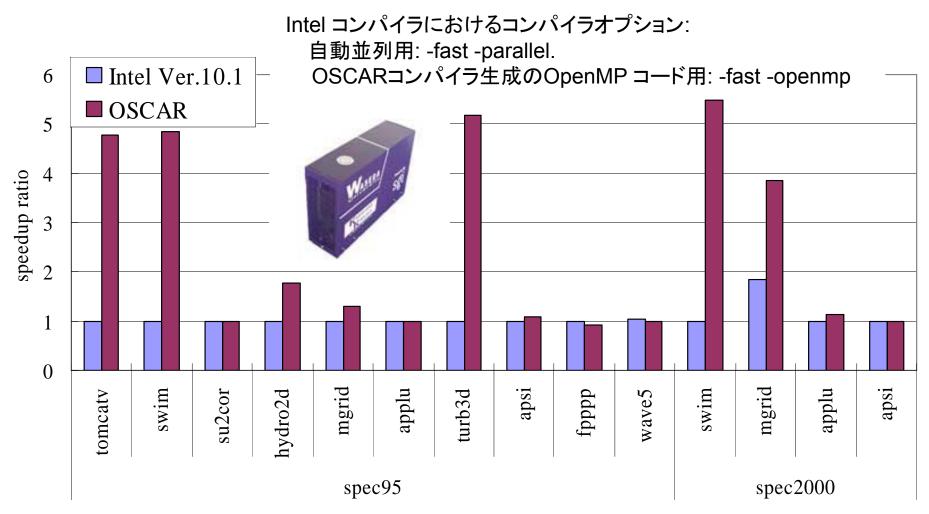

## インテル クアッドコアXeonプロセッサ上での 早稲田大学 OSCARコンパイラの性能

OSCAR コンパイラはインテル最新コンパイラ ver.10.1に比べインテル・マルチコア上で2.09 倍の速度向上

#### インテルMontvaleマルチコアを用いた 16 コアSGI Altix 450 デスクサイドサーバ上での OSCAR コンパイラの性能

OSCAR コンパイラはインテル最新のFortran Itanium Compiler revision 10.1に対し 2.32 倍の速度向上

#### IBMサーバp550q上でのOSCAR並列化コンパイラの性能

8プロセッサコア・マルチプロセッサシステム上で 従来のループ並列化に対し、2.7 倍の高速化 533 MHz ■ ループ並列化 Four I/O Drawers ■ マルチグレイン並列化 adapters share PCIX slots 4 and 5 9 8 speedup ratio 3 0 tomcatv swim |su2cor|hydro2|dmgrid| applu |turb3d| apsi |fpppp |wave5| swim | mgrid | applu | spec95 spec2000

# IBM p690 24 プロセッサハイエンドサーバ上での OSCAR並列化コンパイラ性能

早稲田大学OSCARコンパイラは市販コンパイラより 4.82倍の速度

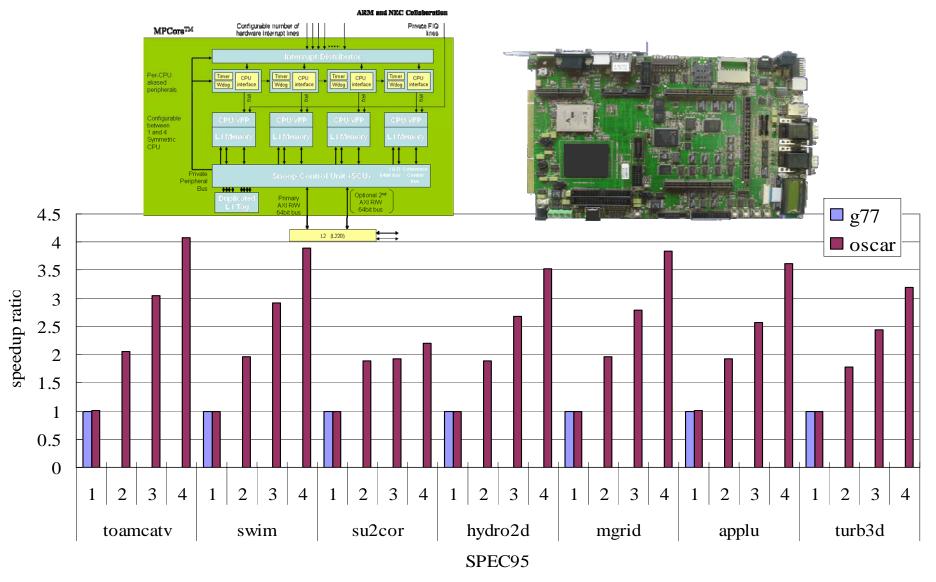

#### NEC/ARM MPCore組込4プロセッサ SMPマルチコア

・ OSCAR コンパイラにより逐次処理に対し、3.48倍の高速化

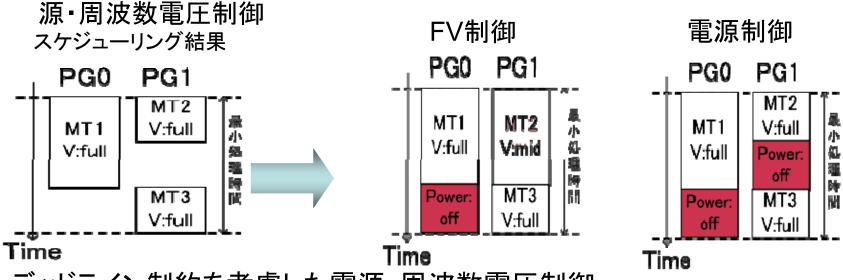

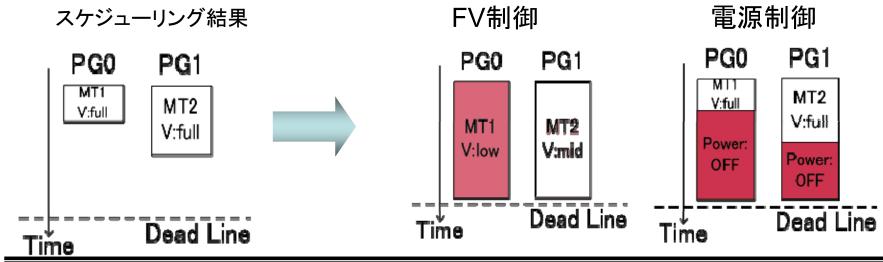

#### 周波数電圧(FV)制御と電源制御による低消費電力化

処理ユニット負荷不均衡時の電

デッドライン制約を考慮した電源・周波数電圧制御

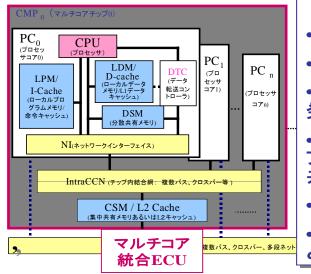

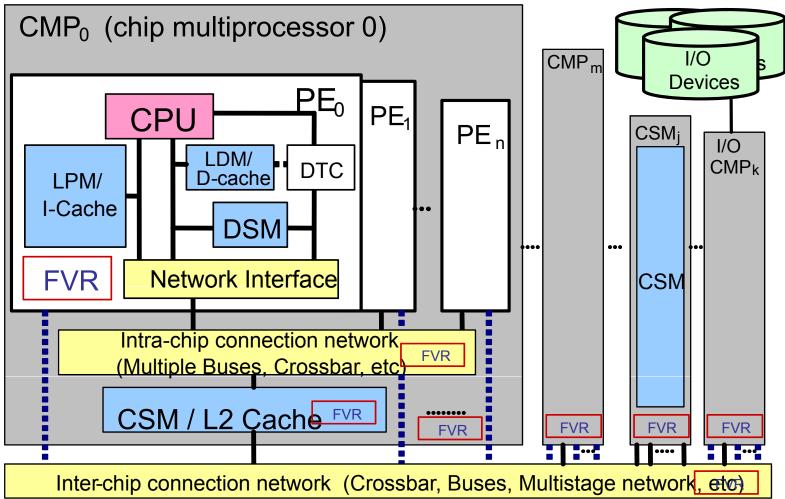

### OSCAR マルチコアアーキテクチャ

CSM: central shared mem. LDM: local data mem.

DSM: distributed shared mem. LPM: local program mem.

DTC: Data Transfer Controller FVR: frequency / voltage control register

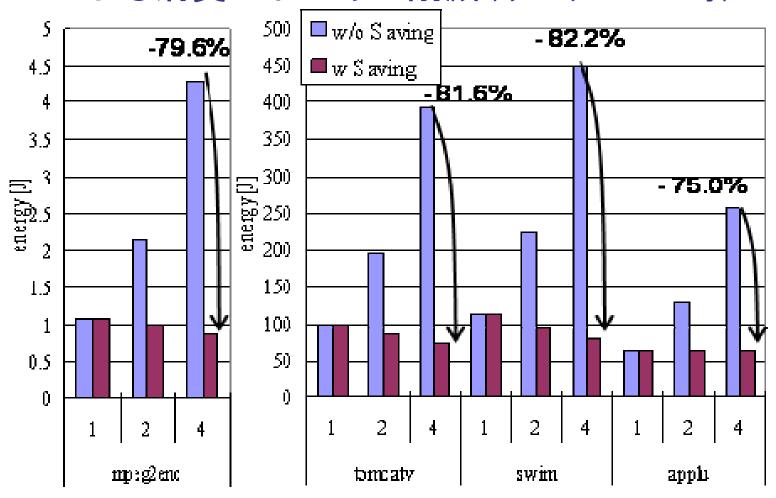

# 電力制御時評価パラメータ設定

- 90nm、400 MHz を想定

- 通常電圧:1.1 V

- 消費電力(CPUのみ、動作): 220 mW

- 消費電力(CPUのみ、リーク): 2.2 mW

- F-V状態

| 状態      | FULL | MID   | LOW   | OFF |

|---------|------|-------|-------|-----|

| 周波数     | 1    | 1/2   | 1 / 4 | 0   |

| 電圧      | 1    | 0.87  | 0.71  | 0   |

| 動作エネルギー | 1    | 3 / 4 | 1/2   | 0   |

| リーク電流   | 1    | 1     | 1     | 0   |

- F-V状態遷移時の遅延

- 動作状態(FULL, MID, LOW)間の遷移: 100µs

- ON/OFF 間の遷移: 200µs

- •コンパイラ内での電力見積もり結果を算出

- •Spec95FP tomcatv, swim, applu を評価

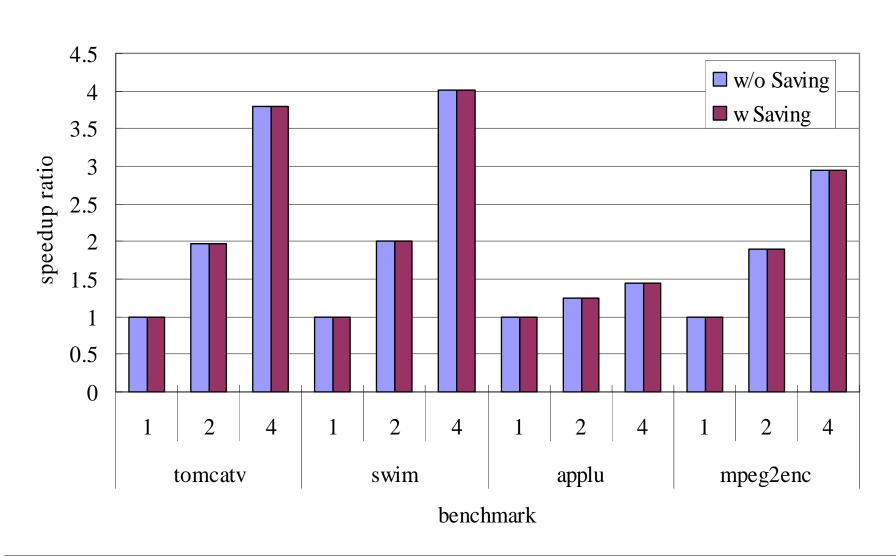

# 最速実行モードの速度向上率

# 実行時間最小スケジューリングモードでの 消費エネルギー

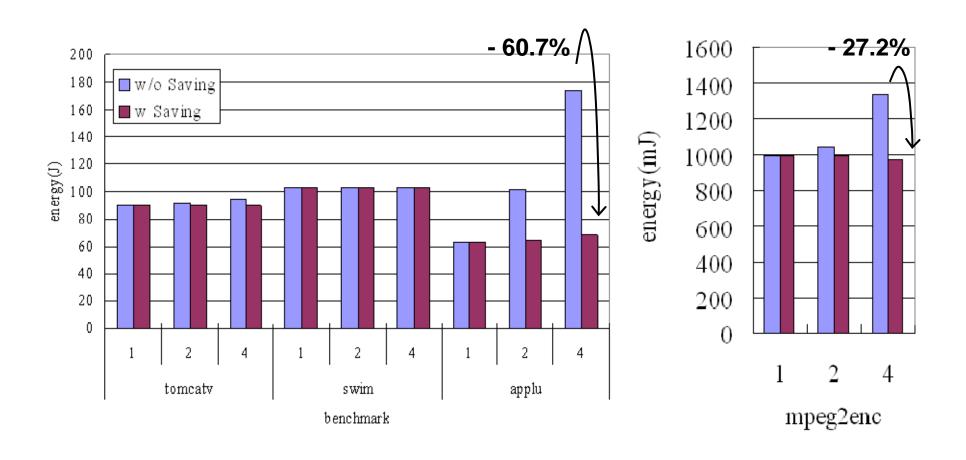

# リアルタイム実行時のコンパイラ制御による消費エネルギー削減(リーク10%時)

コンパイラ制御によるリアルタイム処理時の 低消費電力化(4core, リーク10%)

#### リーク電力変化時のコンパイラ消費電力制御手法の性能

- ・デッドライン = 逐次処理時間 × 0.5

- ・ 4 プロセッサコア

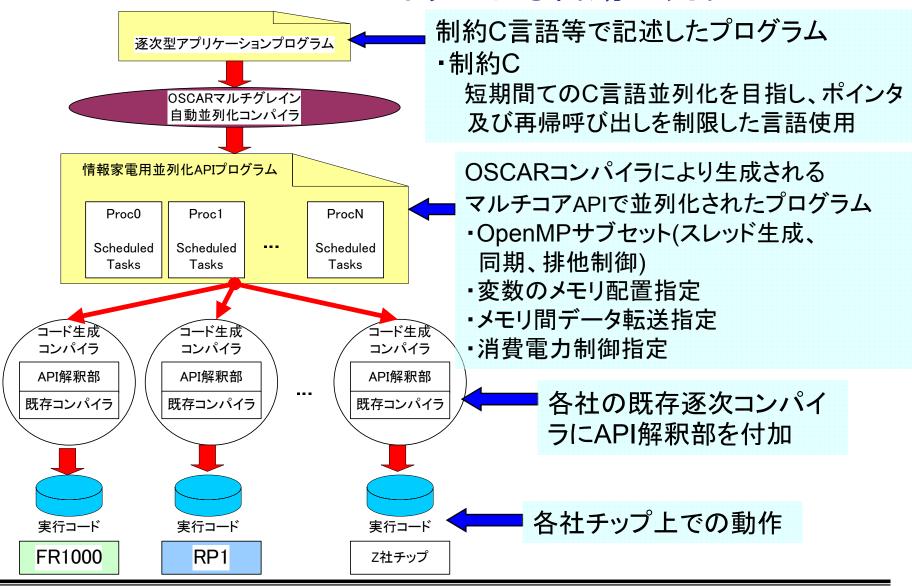

# 情報家電用マルチコア並列化APIを用いたOSCARコンパイラによる自動並列化

# 富士通 FR1000マルチコア

#### 富士通 FR1000マルチコア上での OSCARコンパイラによる並列化性能(策定API利用)

1プロセッサと比較して、4プロセッサで平均3.38倍の速度向上

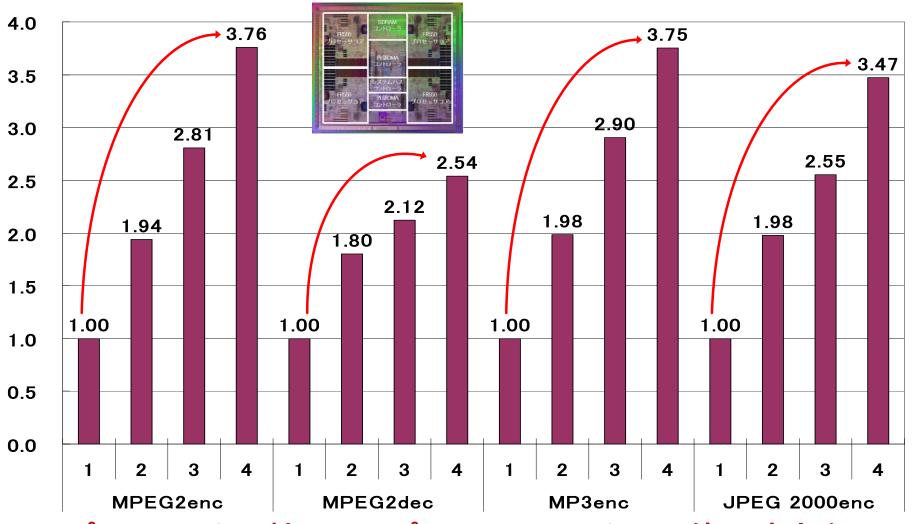

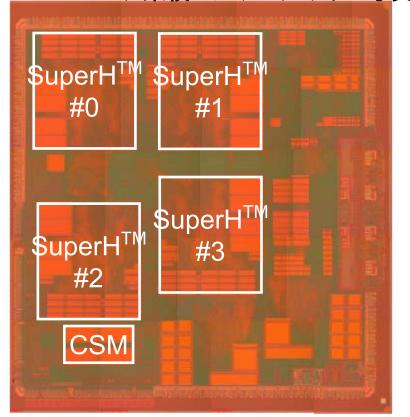

#### 情報家電向けマルチコアRP1(4コア)

RP1 4コア集積マルチコア チップ写真

| プロセス                              | 90nm CMOS, 8層メタル, 3種Vth        |

|-----------------------------------|--------------------------------|

| チップ <sup>°</sup> サイス <sup>*</sup> | 97.6mm² (9.88mm x 9.88mm)      |

| 電源電圧                              | 1.0V(¬7), 1.8/3.3V(I/O)        |

| 消費電力                              | 0.6mW/MHz/CPU @ 600MHz         |

| 動作周波数                             | 600MHz                         |

| CPU性能                             | 4320 MIPS (Dhrystone 2.1)      |

| FPU性能                             | 16.8 GFLOPS                    |

| 命令/データ キャッシュ                      | 32KB 4 ウェイセットアソシアティブ<br>(各CPU) |

**CSM: 128KB**

チップ諸元

ISSCC07発表: ISSCC07 論文番号5.3, Y. Yoshida, et al., "A 4320MIPS Four-Processor Core SMP/AMP with Individually Managed Clock Frequency for Low Power Consumption"

ローカルメモリ

パッケージ

分散共有メモリ

集中共有メモリ

命令8KB/データ16KB(各CPU)

FCBGA 554pin, 29mm x 29mm

URAM:128KB(各CPU)

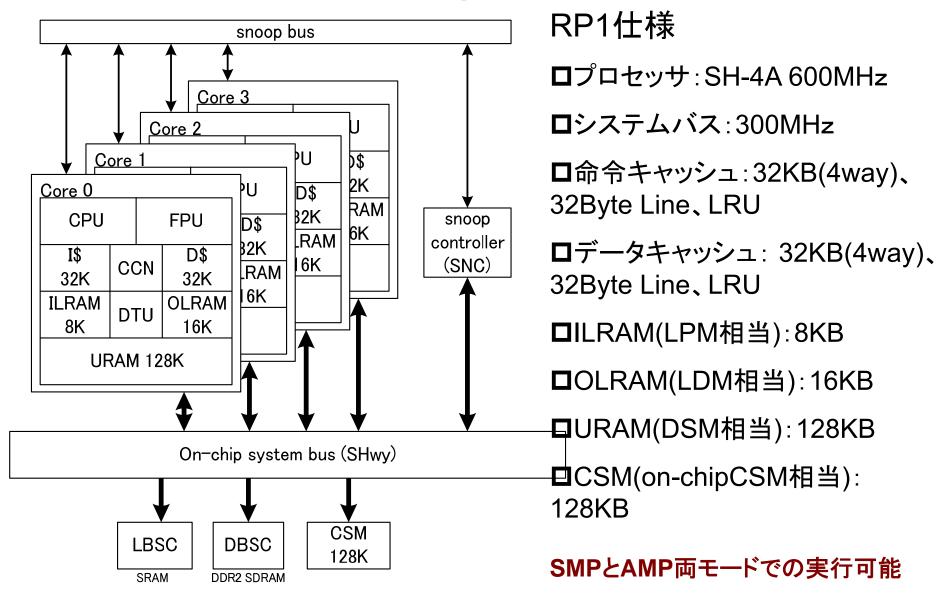

# ルネサス・日立・早大 RP1マルチコア

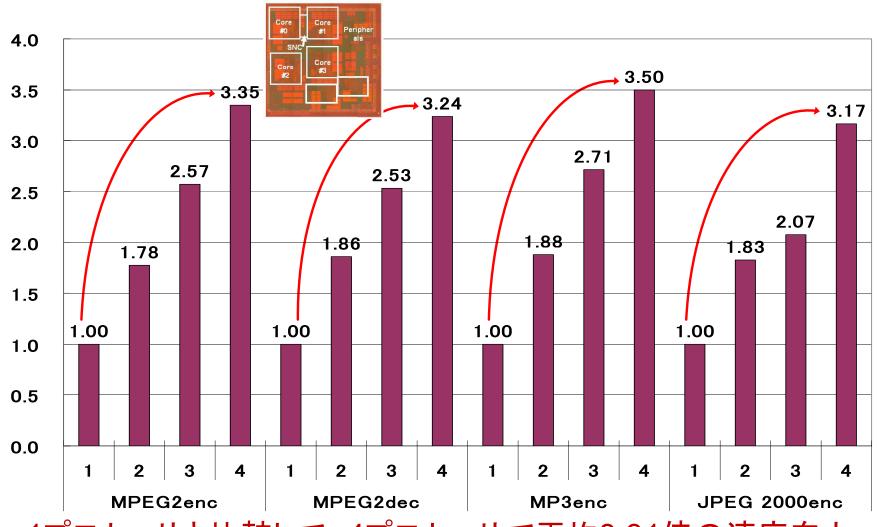

#### 開発マルチコアチップRP1上でのAPIを 用いた制約C自動並列化性能

■ 並列化コンパイラとAPI解釈系を用いたマルチメディア並列処理性能評価

オーディオ圧縮 AAC\*エンコーダ

相 5.0 対 速 度 4.0 3.43 2.70 3.0 1.86 2.0 1.00 1.0 4 プロセッサ数

\*) Advanced Audio Coding: ISOにおいて規格化された 音声圧縮方式

画像のノイズ除去 (組込み向けベンチマーク\*\*)

\*\*) Michigan大による組込みアプリケーション 向けベンチマーク

# 開発RP1マルチコア(4cores)上での並列化コンパイラを用いた並列処理性能(速度向上率)

1プロセッサと比較して、4プロセッサで平均3.31倍の速度向上

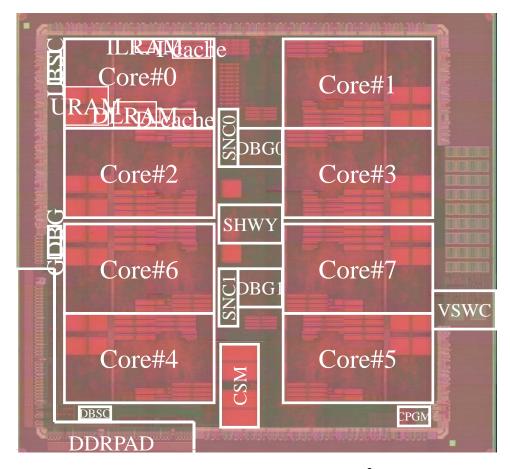

#### RP2 8コア搭載マルチコアLSI

チップ諸元

8コア集積マルチコアLSIチップ写真

| プロセス                              | 90nm CMOS, 8層メタル, 3種Vth                                                                                                                                                                                      |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| チップ <sup>°</sup> サイス <sup>*</sup> | 104.8mm² (10.61mm x 9.88mm)                                                                                                                                                                                  |  |  |

| 電源電圧                              | 1.0V-1.4V(¬7), 1.8/3.3V(I/O)                                                                                                                                                                                 |  |  |

| 動作周波数                             | 600MHz                                                                                                                                                                                                       |  |  |

| CPU性能                             | 8640 MIPS (Dhrystone 2.1)                                                                                                                                                                                    |  |  |

| FPU性能                             | 33.6 GFLOPS                                                                                                                                                                                                  |  |  |

| 低電力制御                             | <ul> <li>・CPU毎に独立した周波数変更</li> <li>・CPUコアのクロックを停止するスリープモード</li> <li>・CPUコアの一部のクロックを停止するがキャッシュコヒーレンシ維持可能なライトスリープモード</li> <li>・CPUコアの電源供給を停止するフル電源遮断モード</li> <li>・URAM以外のCPUコアの電源供給を停止するレジューム電源遮断モード</li> </ul> |  |  |

ISSCC08発表: ISSCC08 論文番号4.5, M.ITO, et al., "An 8640 MIPS SoC with Independent Power-off Control of 8 CPUs and 8 RAMs by an Automatic Parallelizing Compiler"

#### 8 Core RP2 マルチコアのアーキテクチャ

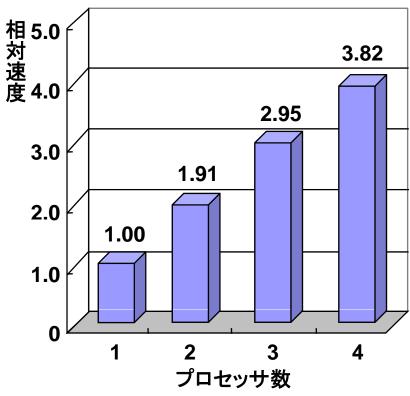

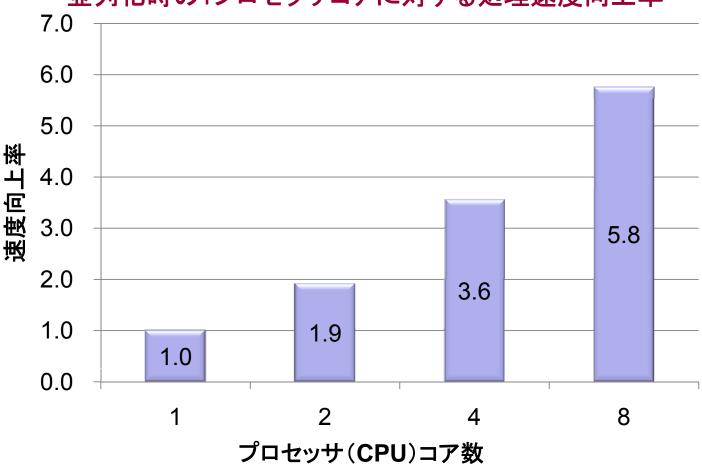

## 開発マルチコア・チップ上での 自動並列化コンパイラを用いた処理速度

オーディオ圧縮(AAC\*エンコード)処理(マルチメディア処理) 並列化時の1プロセッサコアに対する処理速度向上率

\*) Advanced Audio Coding: ISOにおいて規格化された音声圧縮方式

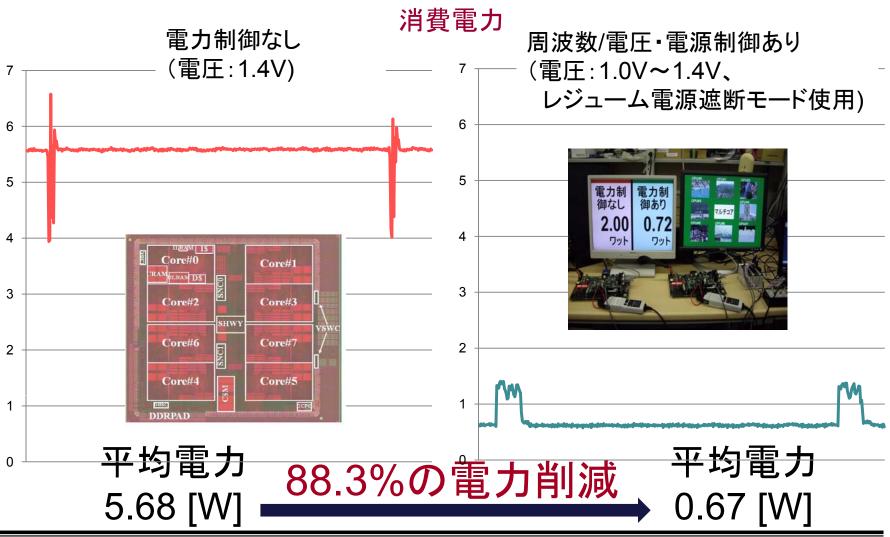

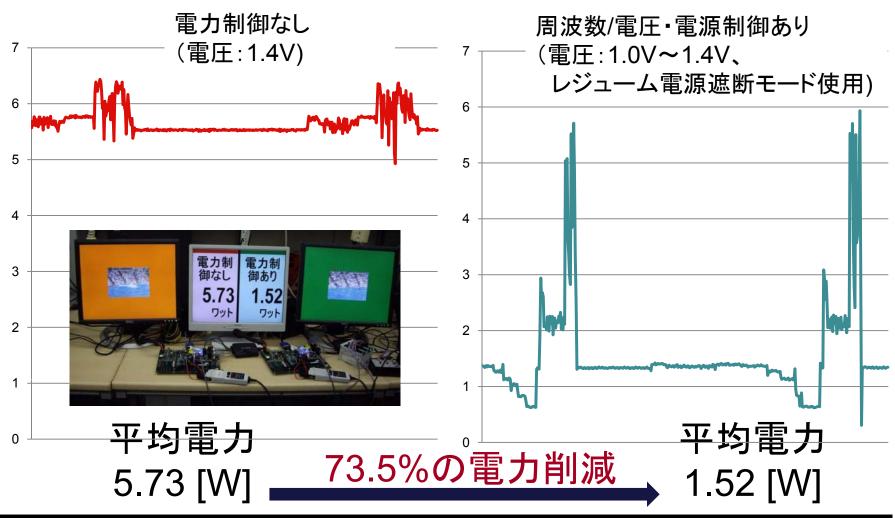

#### 音楽圧縮におけるコンパイラ周波数/電圧・電源制御 による開発チップ上での消費電力削減効果

セキュアオーディオ圧縮(AACエンコード+AES暗号化)処理を8コアで実行時の

# 画像表示におけるコンパイラ周波数/電圧・電源制御による開発チップ上での消費電力削減効果

動画表示(MPEG2デコード処理)を8コアで実行時の消費電力

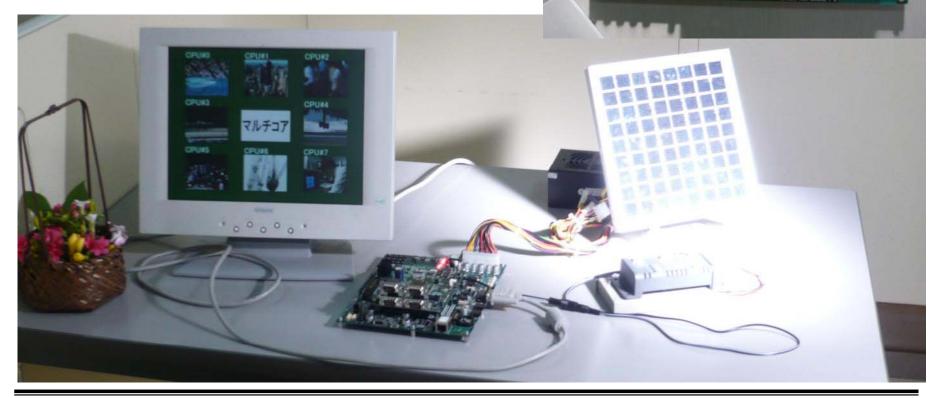

ソーラパネル駆動可能な 低消費電力高性能マルチコア RP2(SH4A 8コア集積)

> クリーンエネルギーで駆動可

▶電力供給が困難な場所での使用可能

▶災害時でも使用可能

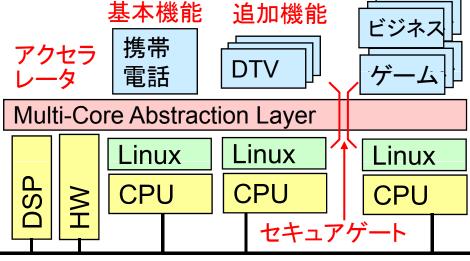

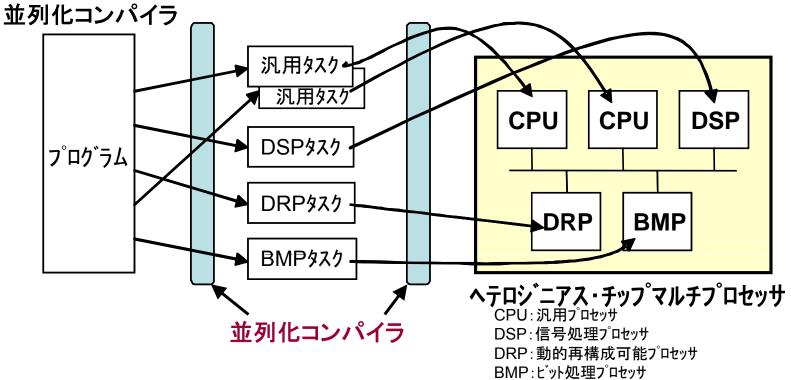

# ヘテロジニアスマルチコア

- コンパイラ協調型先進へテロジニアス・マルチプロセッサ (NEDO 先進へテロジニアスマルチプロセッサ: AHMP)

- NEDO情報家電用へテロジニアスマルチコア

- 多種類の計算エンジン(アクセラレータ)を1チップに集積したSoCアーキテクチャ

- プログラムの並列性を抽出し、各プロセッサの特徴に適したタスクの分割と配置を行う

#### ヘテロジニアスマルチコアアーキテクチャ

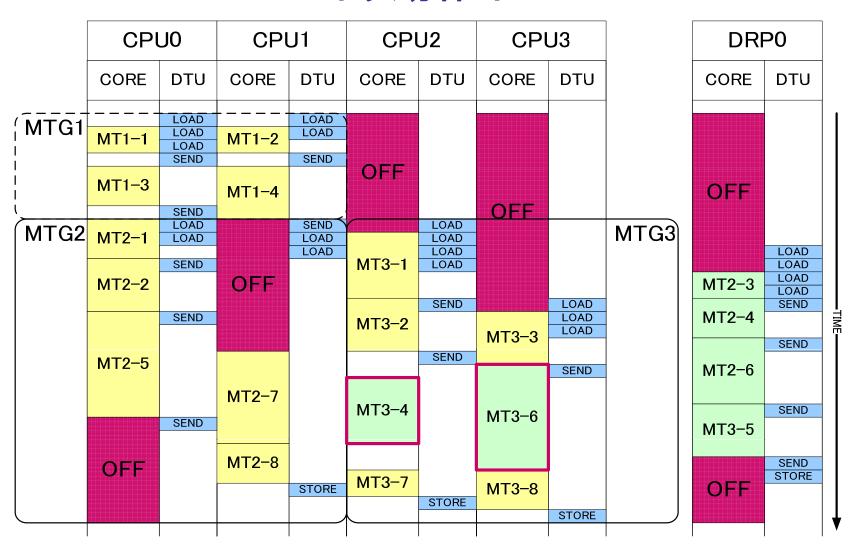

### 粗粒度へテロジニアスタスク並列化 スタティックスケジューリング

### データ転送オーバーラップを含む AHMPコンパイラ動作イメージ

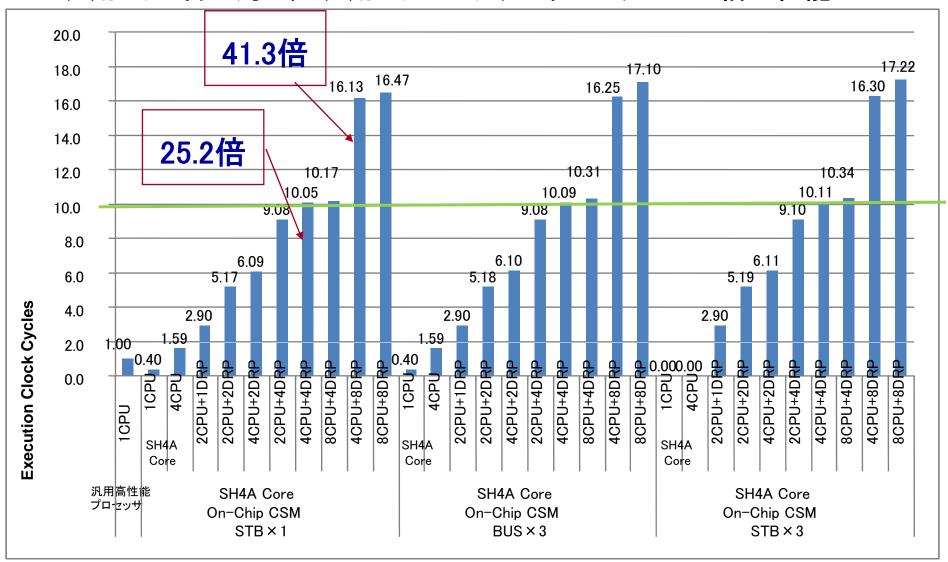

#### ヘテロジニアスマルチコア性能 (オンチップ共有メモリ: 4クロック)

■ 汎用コア1台に対し、4汎用コア+4アクセラレータで25.2倍の性能

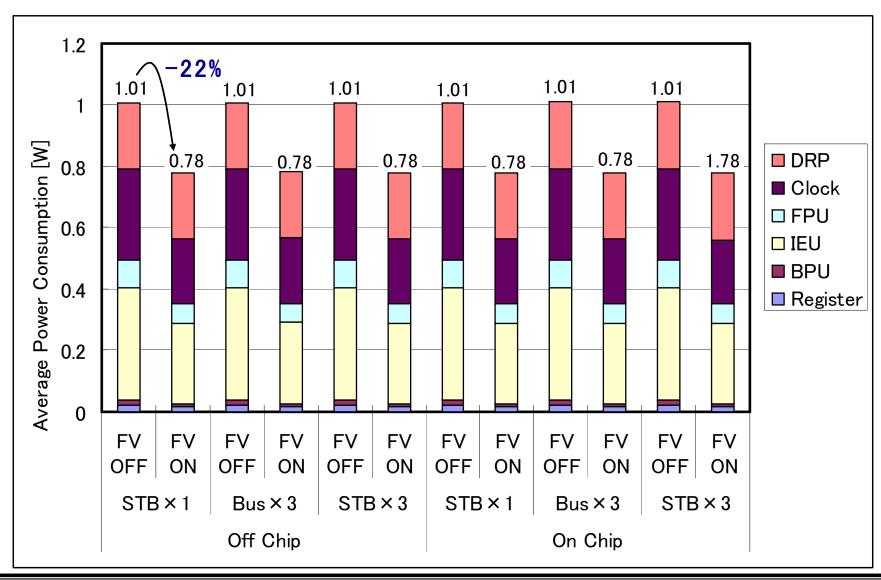

# AHMP低消費電力技術(SH×4+DRP×4)

■ 0.78 W 低消費電力技術により約22%の削減

## まとめ

ゲーム、カーナビ、デジタルTV、DVD、携帯電話などの情報家電から、自動車、スーパーコンピュータまでの幅広い分野でコンパイラ協調型・低消費電力・高実効性能マルチコアプロセッサの重要度が高まる。

- ▶ 並列化コンパイラとアーキテクチャ協調は下記のために必須

- ▶ 優れた価格性能、短ハード・ソフト開発期間、低消費電力

- ▶ 高ソフトウェア生産性、集積度向上にスケーラブルな性能向上

- > 並列処理 API 技術

- ➤ マルチグレイン並列化、メモリ管理、データ転送、消費電力制御、ヘテロマルチコア用APIをNEDOプロジェクト参加6社と開発。これによりOSCARコンパイラは各社のマルチコア用に使用可能(RP1, RP2, FR1000上で動作確認) API詳細仕様: http://www.kasahara.cs.waseda.ac.jp/にて公開

- > コンパイラによる低消費電力制御

- ➤ APIを用いたリアルタイム処理で、8コア使用時に80%以上の消費電力削減

- > コンパイラ自動並列化により処理高速化、開発期間短縮

- ➤ 4コアFR1000,RP1上で2上で3.3倍以上の速度向上