## Modeling Computation for HW/SW Codesign LCPC 2012 Keynote

#### David J. Kuck Software & Services Group

Waseda Univ. Sept. 12, 2012

Copyright © 2012, Intel Corporation. All rights reserved.

# Prologue for my current codesign work

| Торіс                     | 1960s                  | 70s                   | 80s                             | 90s                  | 2000s                          | 2010s   |

|---------------------------|------------------------|-----------------------|---------------------------------|----------------------|--------------------------------|---------|

| Architectur               | Illiac 4 $\rightarrow$ | Burroughs BSP         | Alliant<br>Cedar                | design intui         | Intel<br>tion weak v. g        | lobal 1 |

| e<br>Language             | {Multics}<br>Tranquil, | Lang. focus/extension | ANSI X3H5 ->                    | OpenM                |                                |         |

| —Directive<br>Use tools & | Glypnir                | Parafrase →           | KAP →<br>to optimize for all    |                      | KapTool                        | s →     |

| Model &                   |                        | System Capacity       |                                 |                      | Cape Coo                       | design  |

| Measure                   |                        | →                     | Perfect Club<br>Good methods ha | SPEC<br>ve lifetimes | Intel- Sony<br>Intel -Exascale |         |

| [no<br>guessing]          |                        | Extend useful ideas   |                                 |                      |                                | scale   |

Codesign Goal: Methodology for Designing Systems for a Given Workload that we KNOW will Behave as we Specify.

## Outline

**Prologue & Outline**

- A. System Codesign Example

- **B. Modeling**

- 1. Intro

- 2. Examples

- 3. Power, Energy

- **4. Summary Equations**

- **C.** Measurement and virtual nodes

- **1. Model synthesis tools**

- **D. Example Cape tool results**

**Cost/perf and Energy/perf designs**

**E.** Conclusions

**Extensive, coherent data: fast global analysis**

### **A1. System Behavior – Quality Objectives**

- Stability(unicore, *perf range*, *Data range*)

- Scalability(*freq*, *D*) [ISV: what *D*-range matters?]

- Speedup(*proc*, *D*) [how many cores/chip?]

- Energy, Energy efficiency, Power, ... [many questions]

- Cost initial, operating [how do we define?]

- Combinations of the above [how do we define?]

- Depending on system type

- Server, laptop, handheld, ...

#### Goal: HW/SW Codesign Methodology that handles all of this

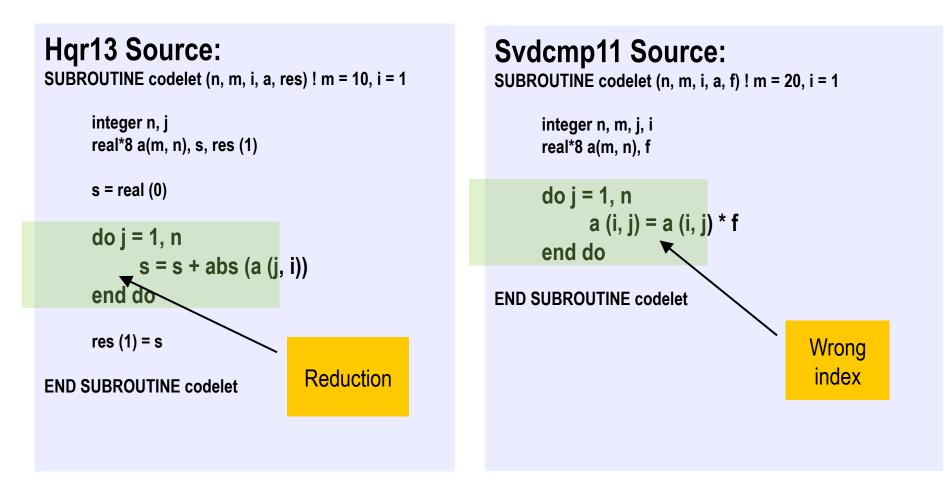

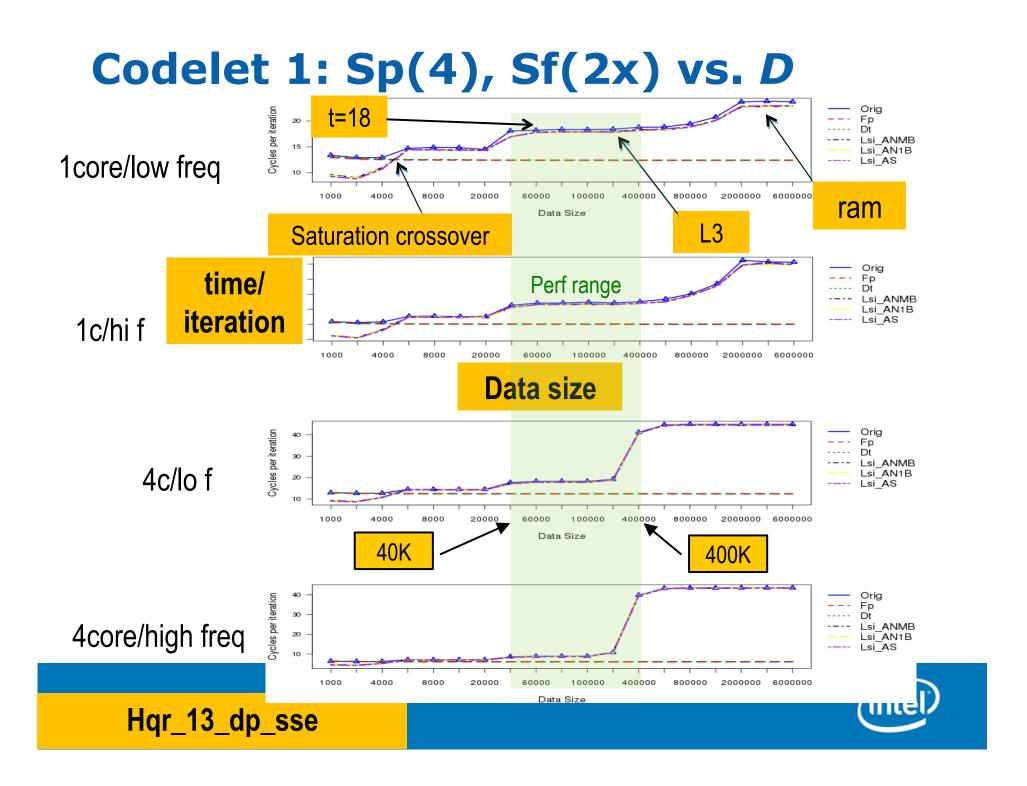

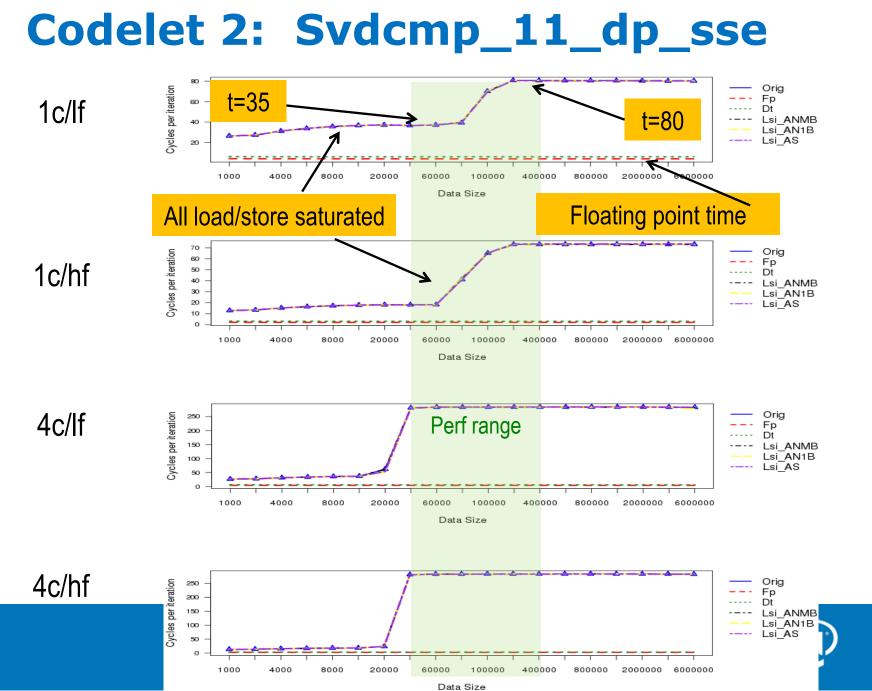

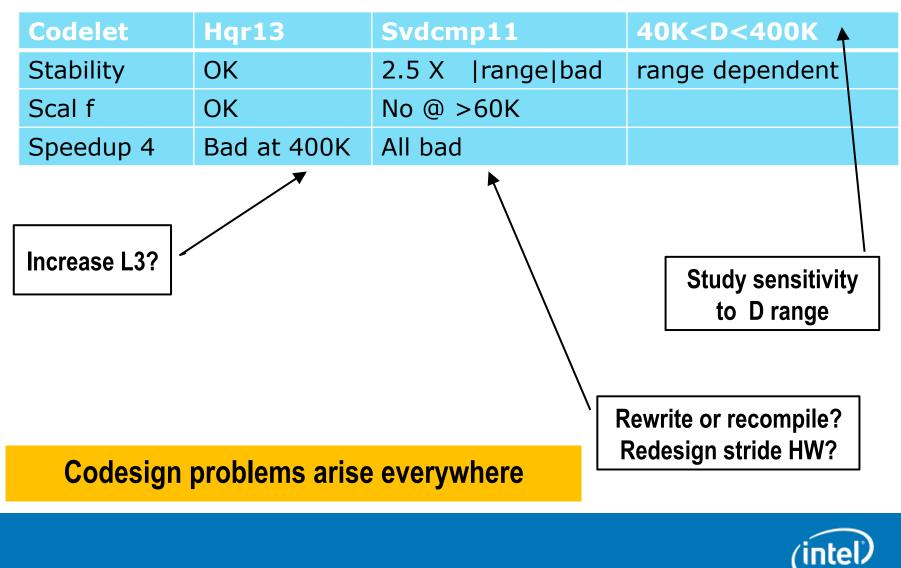

## **Example: Consider 2 NR Codelets**

• Which has good or bad: Stab[D]<2, Scal[f,D] Sp[D]?

# **Quality Results**

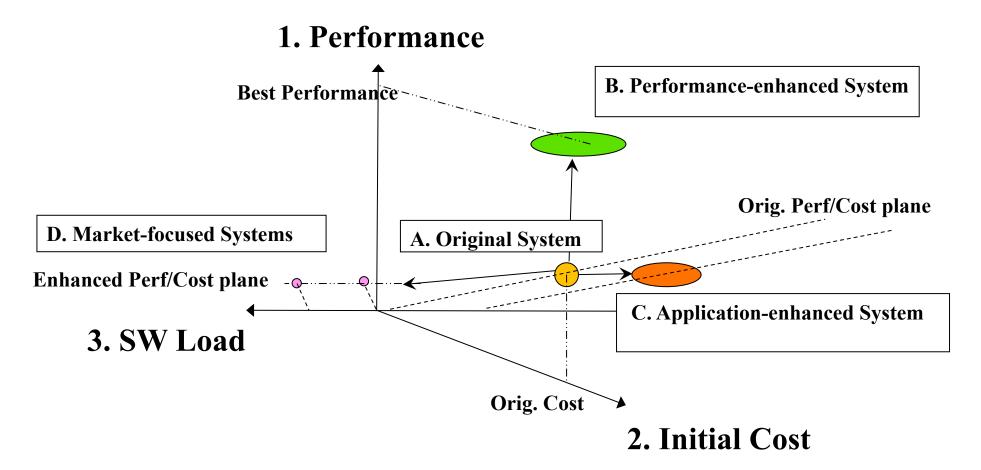

### B.1. Modeling: 4D Codesign Space (w.o. Oper. Cost E)

#### **Physical model characteristics**

Copyright © 2010, Intel Corporation. All rights reserved

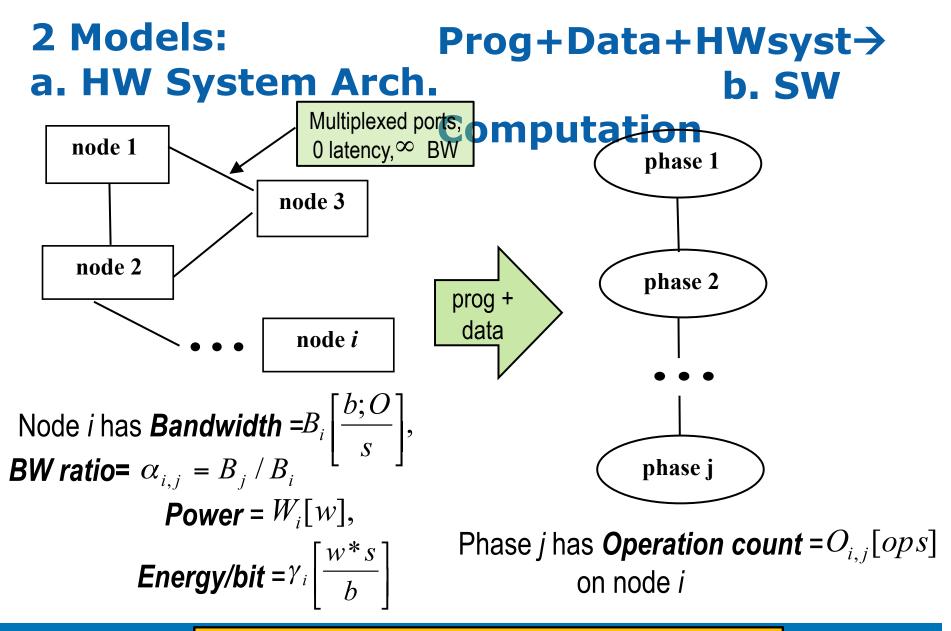

# **A Computation on a System Produces:**

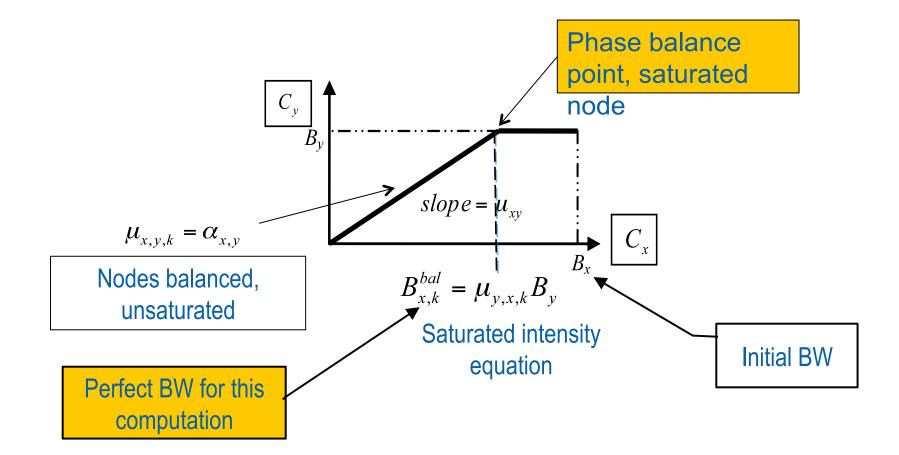

• Capacity Intensity Equation (nodes i,k):  $C_{i,j} = \mu_{ki,j}C_{k,j}$

Each phase saturates one or more nodes

## **Balanced nodes, phase balance point**

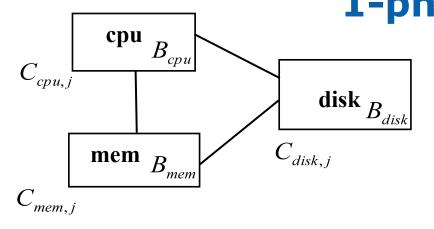

### **B.2. Codesign Examples:** 1-phase, 3-node system

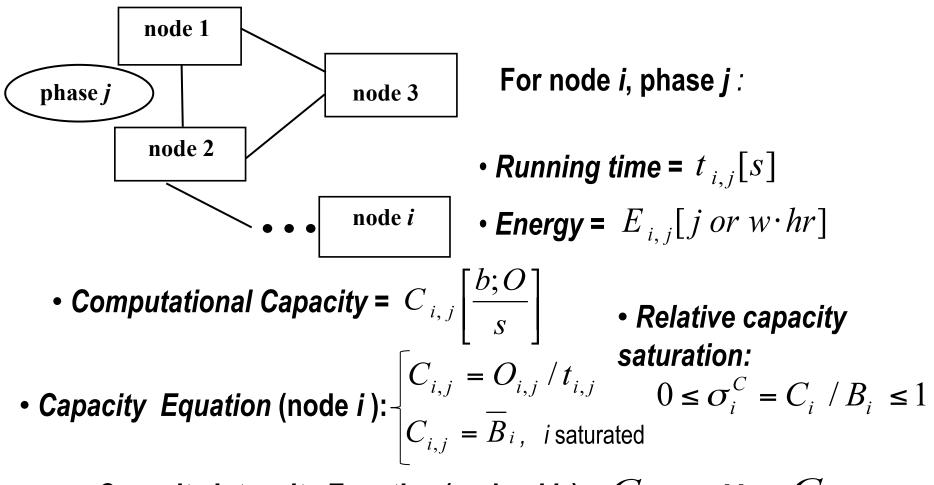

For node *i*, phase *j* :

- **Computational Capacity** =  $C_{i, j} \left| \frac{b}{s} \right|$

- Capacity Equation (node *i*):  $\begin{cases} C_{i,j} = O_{i,j} / t_{i,j} \\ C_{i,j} = \overline{B}_i & i \text{ saturated} \end{cases}$

• Intensity Equation (nodes i,k):  $C_{i,j} = \mu_{ki,j} C_{k,j}$

### How do we systematically increase system performance?

- Focus on saturated node(s)

- Intensity  $\mu_{ki,j}$  is **invariant** if SW is not changed

#### Simple design questions follow

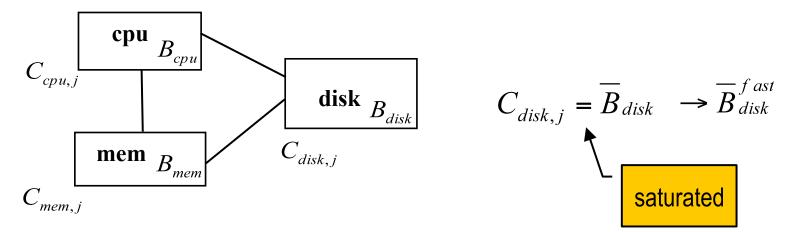

# Ex.1: Systematically boost syst. perf.?

If  $C_{disk,j} = B_{disk}$ , increase disk performance:

- Set saturated node BW to desired performance level  $\rightarrow \overline{B}_{disk}^{fast}$

- Adjust other nodes accordingly  $\rightarrow$  use  $C_{cpu,j} = \mu_{disk-cpu,j} C_{disk,j}$

#### What if performance demand exceeds the fastest cpu or mem available?

**Drive toward**  $B^{waste} = B - C = 0$ , **subject to discrete node values** Copyright © 2010, Intel Corporation. All rights reserved

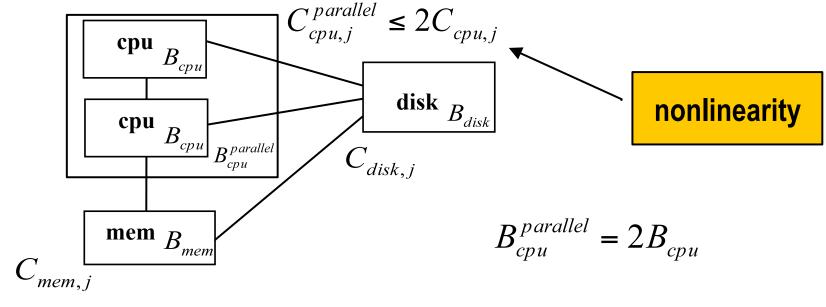

## Ex.2: Perf. demand > fastest node available?

If  $C_{cpu,j}^{goal} > B_{cpu}^{max}$ , use parallel cpu model:

Replicate node – parallel processors or memories add BW

•

$$B_{ik}^{parallel} = B_i + B_k$$

**Parallel capacities lead to** *multirate* nodes,  $C_{cpu,j}^{parallel} \le 2C_{cpu,j}$

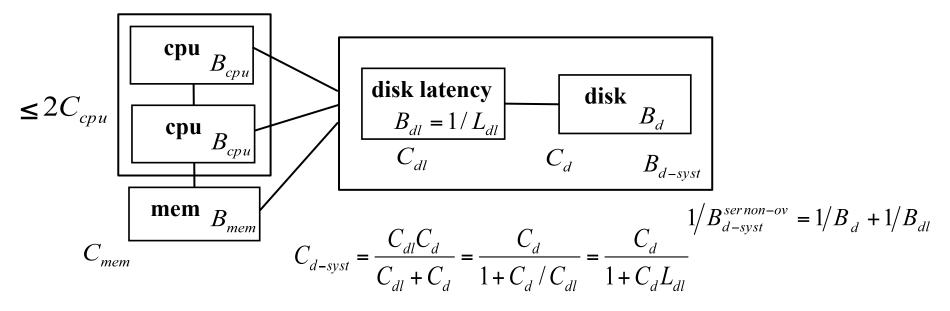

# Ex.3: What if disk has latency?

Latency models: transmission, contention, or rotational delay?

- Physical transmission delay constant, function of wire length

- Serial nodes add reciprocal BWs, nonlinear capacity

$$1/B_{ik}^{sernon-ov} = 1/B_i + 1/B_k$$

$B_{ik}^{serov} = \min\{B_i, B_k\}$

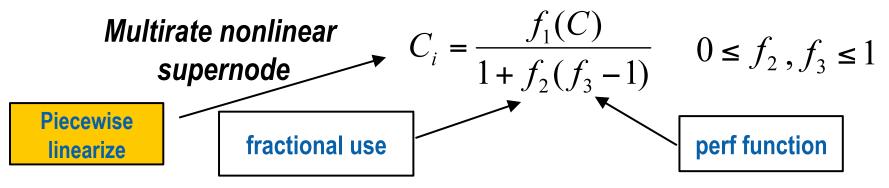

Variable latencies lead to nonlinear *multirate* nodes

## **Summary Internode Equations**

Local Eqs.

Capacity Intensity:

$$C_{i,j} = \mu_{ki,j} C_{k,j} \rightarrow \mu_{ki,j} \overline{B}_k$$

Parallel supernode  $C_{ij}^{parallel} = C_i + C_j$

Serial supernode  $1/C_{ij}^{sernon-ov} = 1/C_i + 1/C_j; \quad C_{ij}^{serov} = \min\{C_i, C_j\}$

System of (nodes X phases) inequalities -> Global Codesign

Copyright © 2010, Intel Corporation. All rights reserved

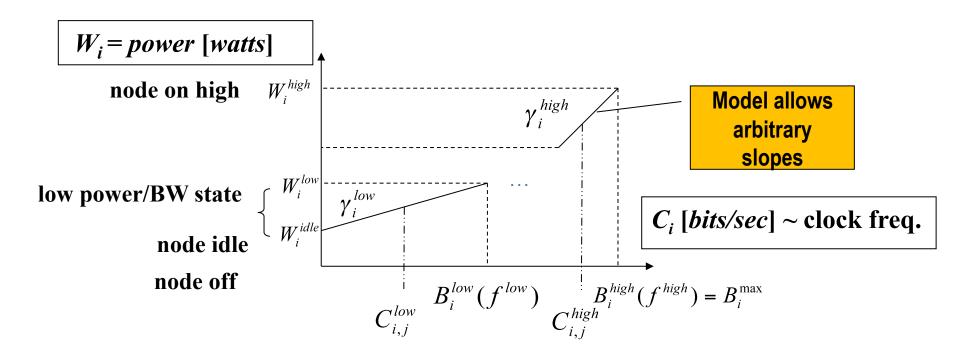

# **B.3. W and E: Average-power model**

$\gamma_{i,j}^{\kappa}$  [E/b] for node i, phase j, power state *k*,  $1 \le k \le s$

Power Equation

$$W_{i,j}^k = \gamma_{i,j}^k C_{i,j}^k + W_i^{kidle}$$

**Combine with architecture codesign model**

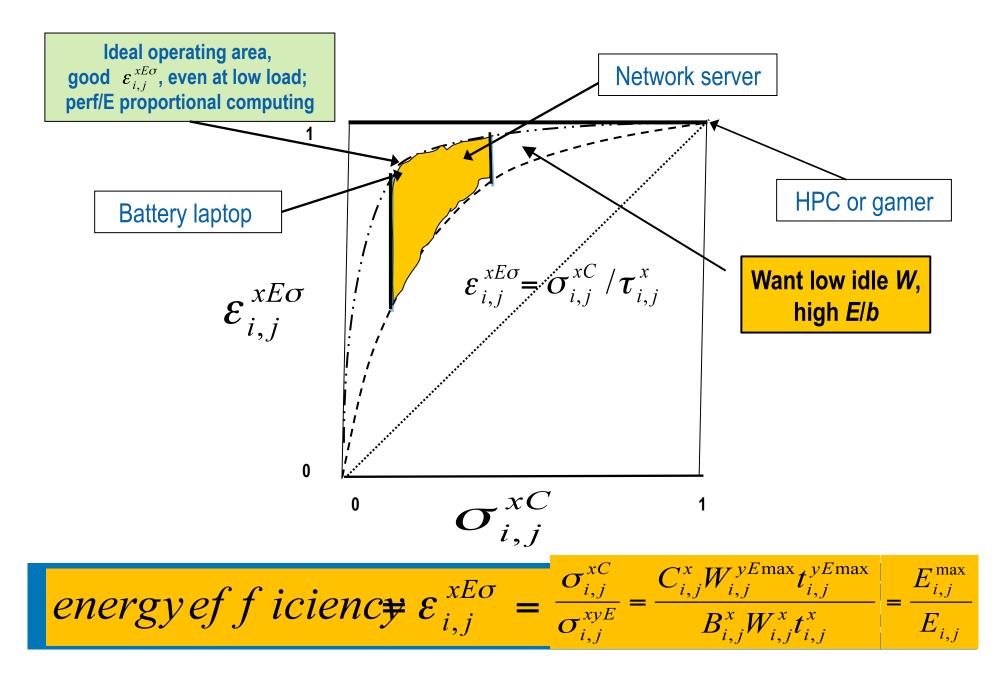

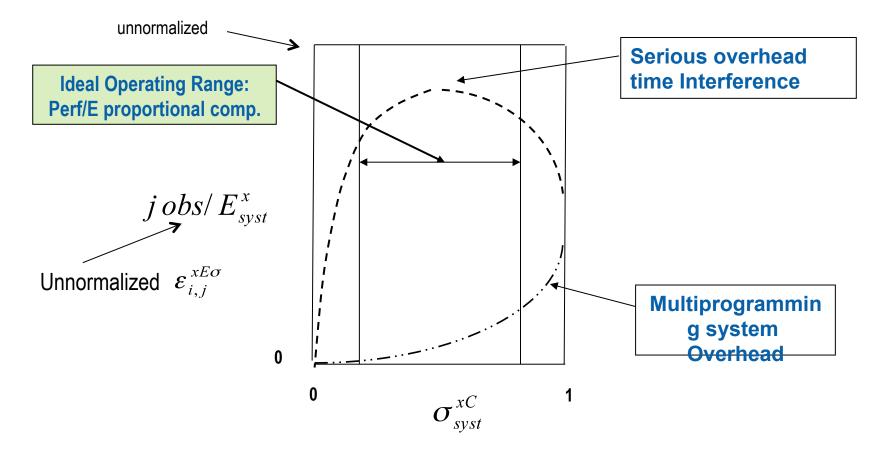

#### **Energy efficiency vs. Capacity Rel. Saturation**

### Multiprogrammed jobs/energy vs. Capacity relative

### saturation

#### "Server consolidation" problem

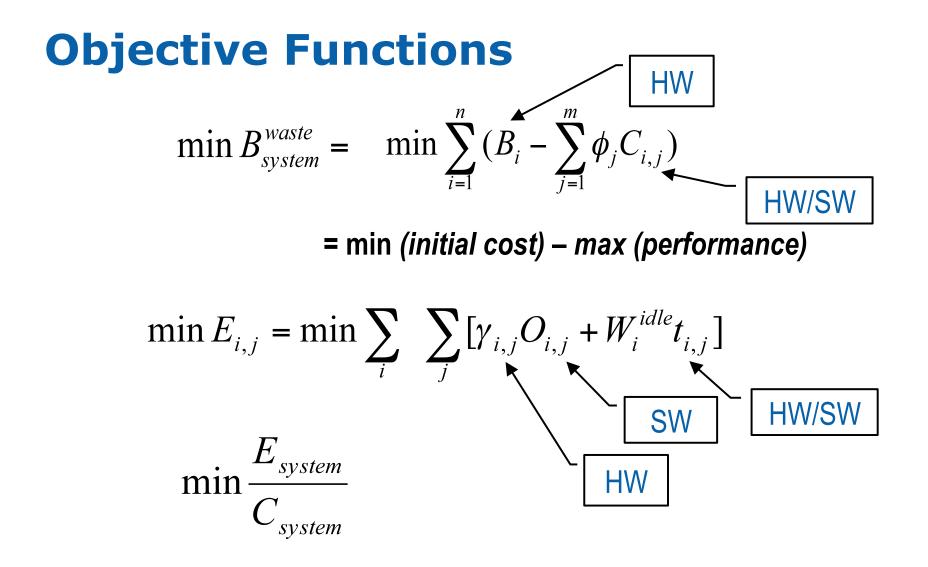

### **B.4. Modeling Summary: Node Property Eqs.**

**Capacity**  $0 \le C_{i,i} = O_{i,i} / t_{i,i} \le B_i^k (f, V) \le B_i^{\max} = \max_i \{C_{i,k}\} - > B_i^{phy}$ 4 Local Eqs. time **Power**  $0 \le W_i = \gamma_i C_i + W_i^{idle} \le W_i^{max}$ node *i*, phase *j* **Energy**  $E_{i,j} = W_{i,j}t_{i,j} = \gamma_{i,j}O_{i,j} + W_i^{idle}t_{i,j}$ • Initial Cost =  $\sum B_i$ 3 Global • Performance =  $\sum \sum f(C_{i,j})$ Eqs. • Operating Cost =  $\sum \sum E_{i,i}$

above + internode equations = complete set

# C. Measurement: sources, types of data

- Simulator

- RTL level: all details, phase=inst or more, very slow

- Functional: less detail, faster

- Numbers very arch-specific, constrains codesign variations

- Math model, e.g. queueing

- Fast, but localized, and may be architecture constrained

- HW counters

- Very fast, fixed meas. points, quirky (defs tricky, changing)

### Single-valued virtual nodes (details following)

- Combine HW/SW at intuitively useful level

- Flexible, allows various architectural mappings

- Measure via binary instrumentation, nopping, ubenchmarks

- Example: mem-mem vector ops: f(stride, length, ... )

#### Input assumptions $\rightarrow$ output interpretation

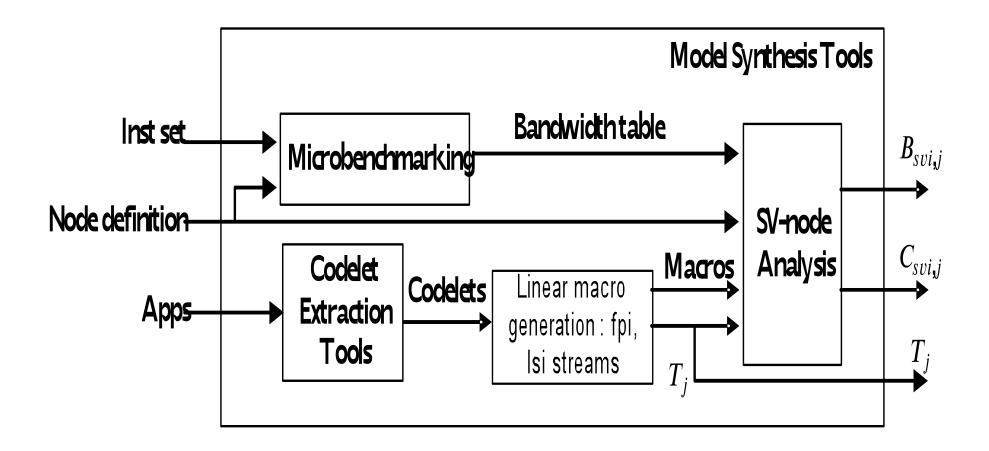

# **Virtual Node Model Synthesis**

Joint work with Intel Exascale Lab, Paris

# **Codelet** $\rightarrow$ **sv-node decomposition**

#### Level

Original program → phases Codelet

Macro

Single rate v-node

#### **Properties**

Irregularities removed, e.g. -alignment, aliasing, ...

Significant time, automatically isolatable, similar µ values, ...

Mutually exclusive inst. seq., i.e. satisfy time linearity test

Similar phy. node execution and memory access, so constant execution rate

#### **Tools list: next foil**

# **SW Tools for sv-node modeling**

- Microbenchmarking node  $B = \max_{k} \{C_{i,k}\}$

- Generation tool

- Capacity analysis <*node,phase*> *C*

- Maqao: static analysis of assembly code

- Decan: dynamic analysis of binary code

- Replace selected instructions, run modified binaries

- Nopping change, kill, or replace op with nop

- Destroys semantics, but gets accurate Capacity values

- Intel Exascale Lab W. Jalby, Versailles

#### **Tools for Application Characterization**

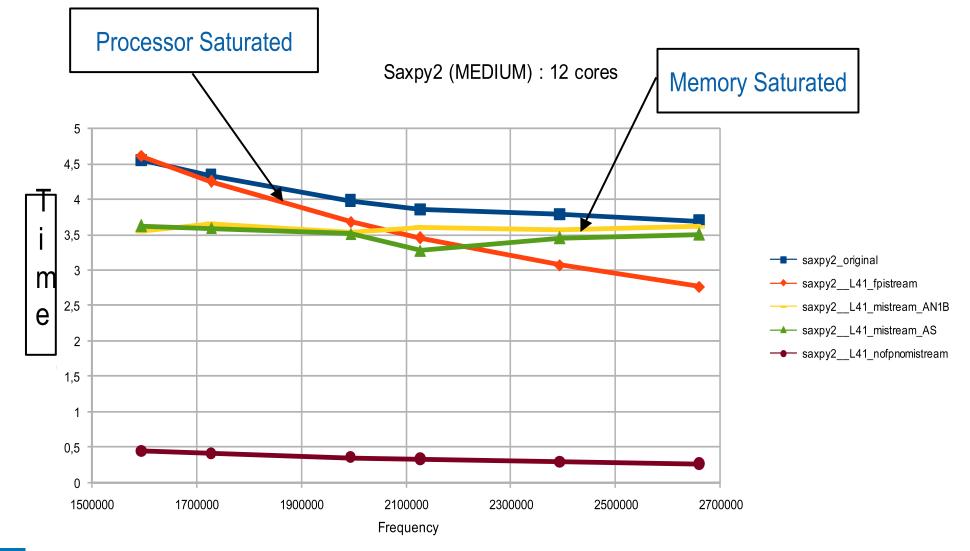

# **Decan: Magma Codelet Behavior (2)**

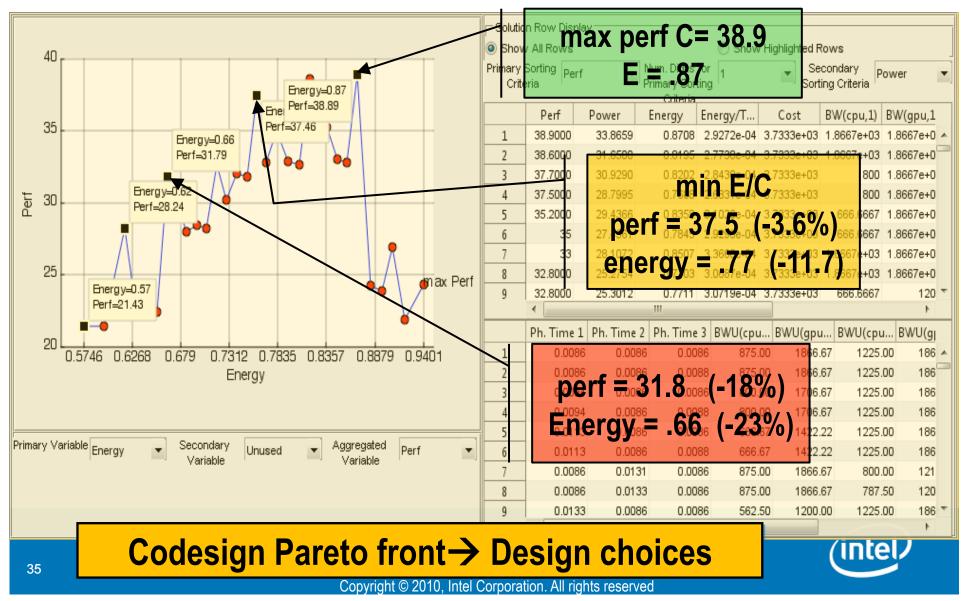

## **D. 3 example problems, Cape solutions**

- 1. Min *cost*, max *perf* codesign problems

- a. Analytical models of critical breaks in codesign space

- b. Cape tool for codesign

- 2. From system set, choose max *perf* (or min *E/C*)

- a. Recommender system for OEM vendor website

- 3. Codesign energy efficient systems

- a. Offline phase analysis predicts future

- → online (*f*, *V*) control governor [ $B^{waste} \rightarrow 0$ ]

- b. min *E* or min *E*/*C* solutions

#### Treat measured $\mu\,$ ratios as constants

# Cape codesign inputs/outputs

#### • Performance

- Minimal thresholds or step ahead: codesign process input

- Bandwidth used units: input/output

#### • Costs

- Initial cost = BW needs, operating cost = E etc.: input/output

- Max limits

- Variable as function of value to buyers of design

#### • Load

- Defined using *node*  $C_{i,j}$ ,  $\mu$ , and saturations

- Data sets  $\rightarrow$  computation program paths: vary phase weights

- Stability of design

- How sensitive are perf and cost to load-usage uncertainty?

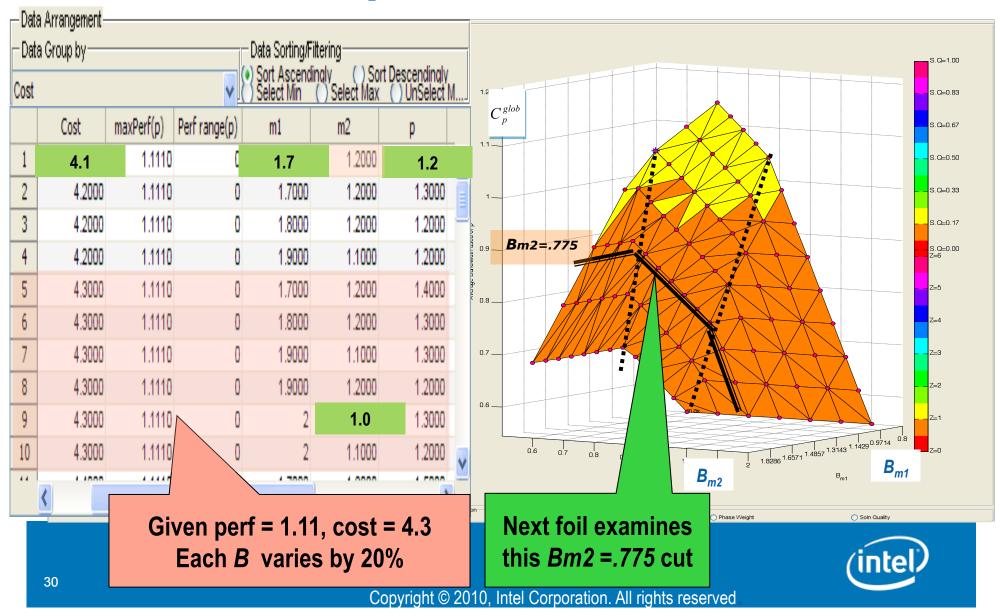

### D.1. Solving cost/perf codesign problems (3node X 2phase) example

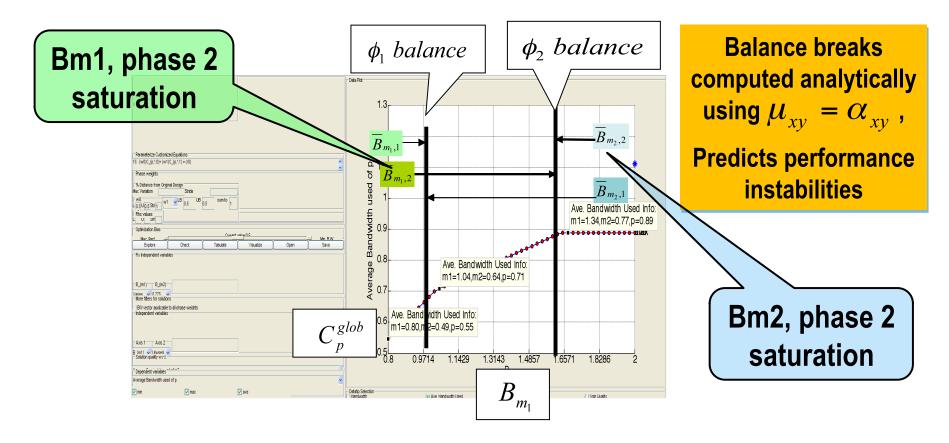

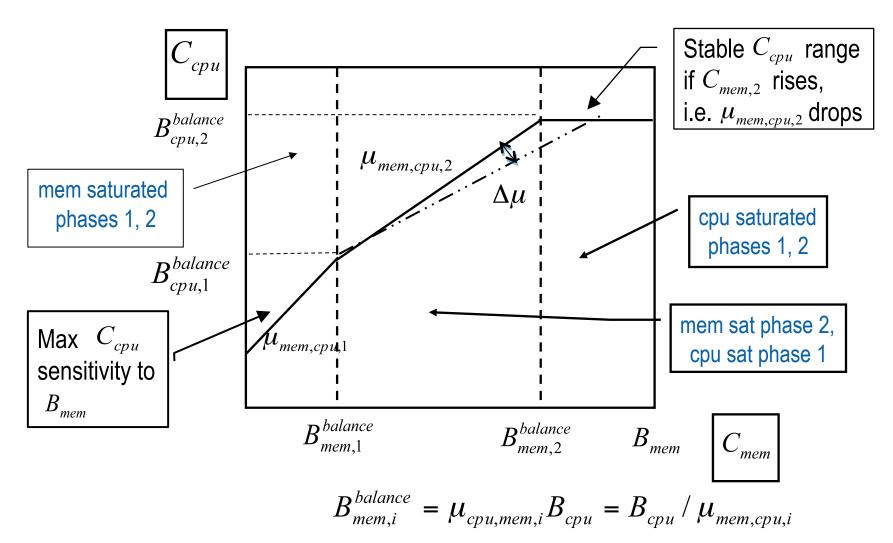

### **D1.** cont. Sensitivity of Performance to the System

**Processor perf vs.**  $B_{m1}$ , showing 3 perf regions;  $B_{m2}$ =.775

### Mem BW vs. Perf. Stability?

## 3-node, 2-phase balance points 📄

## **D.2 Capacity-based Recommender System**

- When a user asks about purchasing a new system

- Current websites give extensive lists, little insight

- Reco tool recommends top choices

- Perf ranking among user's options

- Explains why chosen, based on current SW apps

- v-nodes represent user-specific HW/SW combinations

- OEM customer-support program feature

- Anonymously measuring 8M users continuously

- Run "capacity model" periodically on user's system

- System model constrained

- Apps include all processes running: 1 sec. samples

- Increasing HW nodes selectable

#### Apps usage of system?: Users/OEMs don't understand

## **D.3. Power and Energy Objectives**

- Design-in low power model:  $W_i^{idle}$  ,  $W_i^{max}$  ,  $\gamma_i$

- C/E or C/W proportional computing: use W and E efficiency

- Market needs depend relative loading of systems

- Keep instantaneous power < thermal limit

- Run-time energy control (f,V) scaling, DVFS

- P and C states: C for various idle W levels, P for (f,V) levels

- Energy and time consumed making transitions

- Race-to-Idle: only useful if W model is sufficiently poor

- Conditions easy to state using the model

- Multiprogramming complications if all cores scale together

- Preprocess apps for phase-level (f,V) self-scaling

- OS scheduling interactions, depending on (f,V) resolution

## 3.a Perf vs. Energy for (2x3) model 3 W-states

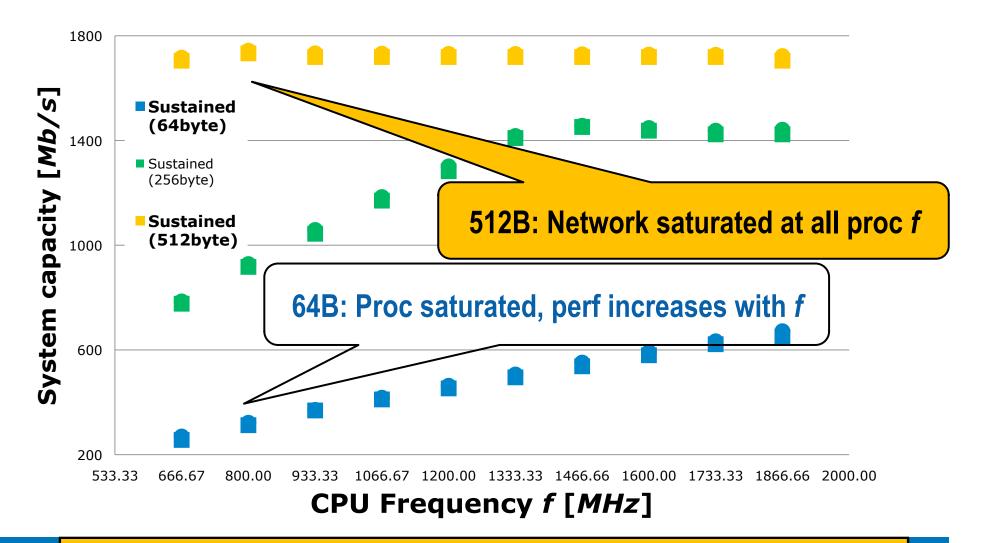

# **3.b Network perf results**

#### Packet size $\rightarrow$ system behavior including E(f,V)

Copyright © 2010, Intel Corporation. All rights reserved

# **E. Summary**

### **1.** Problem: computer system perf, cost, energy, ...

- Pre-Si ← post-Si system analysis

- Architecture, compiler and application codesign

- Is that benchmark in valid form for this arch. simulation?

### 2. Approach: Codesign using HW/SW combinations:

Include

System-wide

Variables

- SW load in HW design

- HW characteristics in SW design

### 3. Break problem into convenient pieces

- HW into nodes (virtual-node flexibility)

- SW into phases (codelets are optimal forms)

- 4. Tools to automate the process

- Aids to human decision makers

Is it really necessary to defer understanding computer behavior to post-Si experimentation – and incur perpetual surprise?

## Key benefits of capacity-based codesign

### 1. Top-down codesign of optimal systems

- Include system-wide interactions

- Mixed fidelity saves modeling effort and simulation time

### 2. Simultaneous use of all "known" load/BW info

- Overcome human-limiting *complexity* via automatic process

- Capture parameter *uncertainties* via sensitivity analysis

### 3. Design focused-system families

- Specialized system-per-market always beats general systems

- Family codesign softens combinatorial explosion

### References

- [JWKA11] William Jalby, et al, *Measuring Computer Performance*, in HPC, Springer, 2011.

- [KFMJ10] Souad Koliai, Fursin, Mosely, Jalby, "DECAN: Decremantal Analysis via Binary Patching, Draft Apr. 2010.

- [Kuck74] D. J. Kuck, "Computer System Capacity Fundamentals," National Bureau of Standards, Technical Note 851, Oct. 1974.

- [KuKu76] D.Kuck, B. Kumar, <u>A system model for computer performance evaluation</u>, SIGMETRICS '76: Proc 1976 ACM SIGMETRICS

- [Kuck78] D.J. Kuck, The Structure of Computers and Computations, Vol. I, John Wiley & Sons, Inc., 1978.

- [Kuck11] DJ Kuck, Computational Capacity-based Codesign of Computer Systems, in HPC, Springer, 2011.

- [LiLS08] Lixia Liu et al, "Analyzing memory access intensity in parallel programs on multicore", *Proc. 22nd ACM ICS*, pp. 359-367, June 2008.

Copyright © 2010, Intel Corporation. All rights reserved