# Poster Session by Ambient GCOE RA, July 14, 2008

# Compiler Cooperative Heterogeneous Multicore Processor"

Akihiro Hayashi, Yasutaka Wada, Hiroaki Shikano, Jun Shirako, Keiji Kimura, Hironori Kasahara Dept. of Computer Science and Engineering

#### Motivation

- Heterogeneous Multicore

- Multicore processor + Accelerator

- Mainstream in Consumer Electoronics

How can we cope with this problem?

Our approach : Parallelizing Compiler and cooperated heterogeneous multicore

Multigrain Parallelization

For Heterogeneous Multicore

Core-grouping on heterogeneous multicore

to realize multigrain parallelization

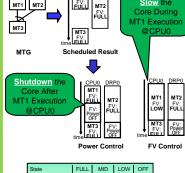

Static Scheduling Scheme

for Heterogeneous Multicore

MT2 MT3

CPU Core For All MT

- Grouped

Accelerator Core

NOT Grouped

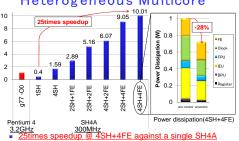

- Simulation Result

- 4CPU+4ACC (Hitachi:300MHz, 0.7W )

- Pentium 4 (Intel:3.2GHz, 72W)

#### Accelerator Core

(CPU Controller) + (Memory) + (ACC)

CPU DTU

- LPM (Local Program Memory) LDM (Local Data Memory)

- DTU (Data Transfer Unit) DSM (Distributed Shared Memory) FVR

**OSCAR** Heterogeneous

Multicore Processor

Chip CSM

CSM (Centralized Shared Memory) (Frequency/Voltage register

We are Proposing OSCAR Parallelizing Compiler and OSCAR Heterogeneous multicore

MT6

MTG

Config

## Multigrain Parallelization

- Exploitation of Multi-level Parallelism

- Coarse-grain Parallelism

- Subroutine, Loop, Basic Block

- Fine-grain Parallelism

- Loop Level Parallelism

- Near-fine-grain Parallelism Statement Level Parallelism

## for (i = 0; i < 100; i ++) { a[i] = b[i] = 0; MT1 func(c); MT2 d = d + a[20]; e = c[5] + a[10]; МТ3

for (i = 0; i < 100; i ++) {

Frequency

Memory

Access Latency

Power Dissipation

(per 1 core)

Processor

Frequency

Cache Size

Pentium 4

MT4

OSCAR Heterogeneous Multicore SH4A FE-GA(DRP)

Details about simulation Evaluated Application : MP3 Encoder

300 MHz (SH,FE,Bus, Memory)

SH4A:150 mW, FE-GA:210 mW (@300MHz, 1.0V, 90nm proces)

Intel Pentium 4

3.2 GHz

Linux 2.2.4 + g77 (u

L1: 8KB, L2: 512 KB

LDM: 1 cycle DSM : 1 cycle(local), 4 cycle(remote) Off-Chip CSM:16 cycle

70 W (@3.2GHz, 1.5V, 0.13 umprocess)

- OSCAR Compiler Generates Hierarchically-Clustered Macro-Tasks (MT)

- Subroutine Block(SB) Basic Block(BB)

- Loop Block(RB)

- Macro-Task Graph (MTG)

- Task Graph considering Control-Flow, Data-Dependency

## Performance on a OSCAR Heterogeneous Multicore

Optimization for higher throughput

All Accelerator MT is NOT always assigned to DRP

- 0.7W:28% Power reduction by Compiler Control

### Power Reduction Scheme For Low Power Consumption

Fastest Execution Mode

**Compiler achieves** low power dissipation by controlling appropriate F/V state for each MT

#### Conclusions

- Parallelizing Compiler and cooperated heterogeneous multicore

- Effective use of accelerator

- Controlling approproate F/V state

- Realize High -performance, Low power dissipation

- 4SH+4FE @300MHz = Pentium 4 @3.2GHz with 1/100 power dissipation

- **Future Work**

- Applying our method to real -chip

Waseda University Global COE Program

"International Research and Education Center for Ambient SoC"